Modern SoCs can be complex with hundreds to thousands of IP blocks, so there’s an increasing need to have a front-end build and assembly methodology in place, eliminating manual steps and error-prone approaches. I’ve been writing about an EDA company that focuses on this area for design automation, Defacto Technologies, and … Read More

Electronic Design Automation

Siemens EDA Outlines Strategic Direction for an AI-Powered, Software-Defined, Silicon-Enabled Future

In a keynote delivered at this year’s Siemens EDA User2User event, CEO Mike Ellow presented a focused vision for the evolving role of electronic design automation (EDA) within the broader context of global technology shifts. The session covered Siemens EDA’s current trajectory, market strategy, and the changing landscape … Read More

Cadence at the 2025 Design Automation Conference #62DAC

Cadence, a DAC 2025 industry sponsor, will exhibit in booth 1609 at the 62nd Design Automation Conference at San Francisco’s Moscone West Convention Center.

Highlights:

Paul Cunningham, SVP and GM of the System Verification Group, Cadence, will speak at Cooley’s DAC Troublemaker Panel. This discussion will be an open… Read More

Verific Design Automation at the 2025 Design Automation Conference

Rick Carlson, Verific Design Automation’s Vice President of Sales, is an EDA trends spotter. I was reminded of his prescience when he recently called to catch up and talk about Verific’s role as provider of front-end platforms powering an emerging EDA market.

Verific, he said, is joining forces with a group of well-funded startups… Read More

Video EP8: How Defacto Technologies Helps Customers Build Complex SoC Designs

In this episode of the Semiconductor Insiders video series, Dan is joined by Chouki Aktouf, CEO and Founder of Defacto Technologies. Dan explores the challenges of building complex SoCs with Chouki, who describes challenges around managing complexity at the front end of the process while staying within PPA requirements and … Read More

ChipAgent AI at the 2025 Design Automation Conference #62DAC

The semiconductor world is gathering at DAC 62, and ChipAgents AI is coming ready to show why agentic AI is the missing piece in modern RTL design and verification. Whether you’re drowning in terabytes of waveform data, grinding toward 100% functional coverage, or hunting for ways to accelerate time-to-market, our sessions and… Read More

Anirudh Fireside Chats with Jensen and Lip-Bu at CadenceLIVE 2025

Anirudh (Cadence President and CEO) had two fireside chats during CadenceLIVE 2025, the first with Jensen Huang (Founder and CEO of NVIDIA) to kick off the show, and later in the day with Lip-Bu Tan (CEO of Intel). Of course Jensen and Lip-Bu also turn up for other big vendor shows but I was reminded that there is something special about… Read More

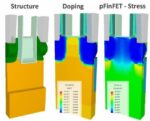

TCAD for 3D Silicon Simulation

Semiconductor fabs aim to have high yields and provide processes that attract design firms and win new design starts, but how does a fab deliver their process nodes in a timely manner without having to run lots of expensive silicon through the line? This is where simulation and TCAD tools come into play, and to learn more about this… Read More

Breker Verification Systems at the 2025 Design Automation Conference #62DAC

Breker Verification Systems Plans Demonstrations of its Complete Synthesis and SystemVIP Library and Solutions Portfolio

Attendees who step into the Breker Verification Systems booth during DAC (Booth #2520—second floor) will see demonstrations of its Trek Test Suite Synthesis and SystemVIP libraries and solutions portfolio.… Read More

The SemiWiki 62nd DAC Preview

After being held in San Francisco since the pandemic the beloved Design Automation Conference will be on the move again. In 2026 DAC will be held in Huntington Beach. For you non-California natives, Huntington Beach is a California city Southeast of Los Angeles. It’s known for surf beaches and its long Huntington Beach Pier.… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot