The explosive growth of large language models (LLMs) has created substantial new requirements for chip-to-chip interconnects. These very large models are trained in high-performance data centers. Multiple accelerators need to work seamlessly to make all this possible as the bandwidth between accelerators directly impacts… Read More

Electronic Design Automation

Video EP5: A Discussion of Photonic Design Challenges and Solutions with Keysight

In this episode of the Semiconductor Insiders video series, Dan is joined by Muhammad Umar Khan, Product Manager for Photonics Design Automation Solutions at Keysight Technologies. Muhammad describes the primary design challenges of photonic design with Dan. These include accurate models and a uniform methodology… Read More

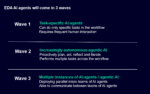

EDA AI agents will come in three waves and usher us into the next era of electronic design

Author: Niranjan Sitapure, AI Product Manager, Siemens EDA

We are at a pivotal point in Electronic Design Automation (EDA), as the semiconductors and PCB systems that underpin critical technologies, such as AI, 5G, autonomous systems, and edge computing, grow increasingly complex. The traditional EDA workflow, which includes… Read More

Webinar – Achieving Seamless 1.6 Tbps Interoperability with Samtec and Synopsys

It is well-known that AI is upending conventional wisdom for system design. Workload-specific processor configurations are growing at an exponential rate. Along with this is an exponential growth in data bandwidth needs, creating an urgency for 1.6T Ethernet. A recent SemiWiki webinar dove into these issues. Synopsys and … Read More

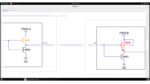

Safeguard power domain compatibility by finding missing level shifters

In the realm of mixed signal design for integrated circuits (ICs), level shifters play a critical role for interfacing circuits that operate at different voltage levels. A level shifter converts signal from one voltage level to another, ensuring compatibility between components. Figure 1 illustrates a missing level shifter… Read More

Leveraging Common Weakness Enumeration (CWEs) for Enhanced RISC-V CPU Security

As RISC-V adoption accelerates across the semiconductor industry, so do the concerns about hardware security vulnerabilities that arise from its open and highly customizable nature. From hardware to firmware and operating systems, every layer of a system-on-chip (SoC) design must be scrutinized for security risks. Unlike… Read More

Metal fill extraction: Breaking the speed-accuracy tradeoff

As semiconductor technology scales and device complexity increases, accurately modeling the parasitic effects of metal fill has become critical for circuit performance, power integrity, and reliability. Metal fill is a crucial part of the manufacturing process, ensuring uniform layer density, improving planarization,… Read More

Video EP4: A Deeper Look at Advanced Packaging & Multi-Die Design Challenges with Anna Fontanelli

In this episode of the Semiconductor Insiders video series, Dan is once again joined by Anna Fontanelli, founder and CEO of MZ Technologies. In this discussion, more details of the challenges presented by advanced packaging and multi-die design are explored. Anna provides details of what’s involved in architectural … Read More

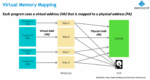

RISC-V Virtualization and the Complexity of MMUs

In the early days of RISC-V adoption, applications were microcontroller-centric with no need for virtualization support. But horizons expanded and now RISC-V is appearing in application processors, very much needing to be able to virtualize multiple apps concurrently. Take another step forward to datacenter servers running… Read More

Video EP3: A Discussion of Challenges and Strategies for Heterogeneous 3D Integration with Anna Fontanelli

In this episode of the Semiconductor Insiders video series, Dan is joined by Anna Fontanelli, founder and CEO of MZ Technologies. Anna explains some of the substantial challenges associated with heterogeneous 3D integration. Dan then begins to explore some of the capabilities of GenioEVO, the first integrated chiplet/package… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center