Traditional, rule based, RC extractors rely on a substantial base of assumptions, which are increasingly proving unreliable. Having accurate RC extraction results for parasitic R’s and C’s is extremely important for ensuring proper circuit operation and for optimizing performance and power. Advanced process nodes are making… Read More

Electronic Design Automation

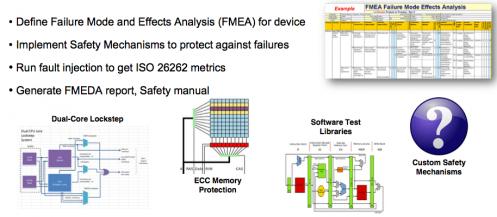

Functional Safety – the Analytics

ISO 26262 is serious stuff, the governing process behind automotive safety. But, as I have observed before, it doesn’t make for light reading. The standard is all about process and V-diagrams, mountains of documentation and accredited experts. I wouldn’t trade a word of it (or my safety) for a more satisfying read, but all that … Read More

EDA CEO Outlook 2018 Partly Cloudy

The funniest line of the EDA CEO Outlook event was that we should rename our Amazon Echos Wally. Yes Wally is that smart and he remembers pretty much everything. I wish I could rename my Echo Wally because my daughter in-law is named Alexa so we have to turn it off when she is over. The discussion took an interesting turn with EDA in the … Read More

Enabling A Data Driven Economy

The theme of this year CDNLive Silicon Valley keynote given by Cadence CEO, Lip-Bu Tan evolves around data and how it drives Cadence to make a transition from System Design Enablement (SDE) to Data Driven Enablement (DDE). Before elaborating further, he noted on some CDNLive conference statistics: 120 sessions, 84% done by users,… Read More

HCM Is More Than Data Management

While tracking Moore’s Law has become a more expensive and difficult endeavor in the HPC design, the mobile SOC design space is also increasingly heterogeneous and complex. Strict safety guidelines such as the ISO-26262 being imposed in the automotive applications further exacerbate the situation.

Looking closer into the … Read More

Is there anything in VLSI layout other than “pushing polygons”? (8)

The year is 1999 and I decided that is time to try something else in layout. In 1989 in Israel I was part of the biggest chip in the world, the Motorola DSP9600. In 1998 in Canada I was part of the biggest Synchronous DRAM in the world, it was time to try analog/mixed signal/RF projects.

The opportunity came from PMC Sierra who already had… Read More

Embracing Architectural Intent

During DVCon 2018 in San Jose, one topic widely covered was the necessity of describing and capturing intent. Defining our design intent up-front is crucial to the overall success of a design implementation. It is not limited to applying a process level intent, such as the use of verification intent with embedded assertions in … Read More

Emulation Outside the Box

We all know the basic premise of emulation: hardware-assisted simulation running much faster than software-based simulation, with comparable accuracy for cycle-based 0/1 modeling, decently fast setup, and comparably fine-grained debug support. Pretty obvious value for running big jobs with long tests. But emulators tend… Read More

EDA CEO Outlook 2018

The EDA CEO outlook took an interesting turn last night but before I get into that I will offer a few comments about the start of the show. I attend this event every year for the content but also for the networking. It isn’t everyday you get to hang out with semiconductor industry elite and have candid conversations over food and drinks.… Read More

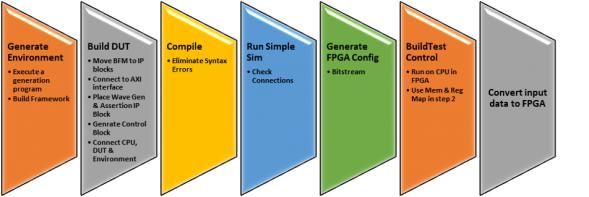

The 4th Way Beyond Simulation, FPGA Synthesis, and Emulation

As verification continues to be a key ingredient in successful design implementation, new approaches have been tried to balance cost, time to results and comprehensive analysis in designs that require large patterns in some application like Image Processing. Simulation environments are well proven, and designers tend to … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center