At the recent DesignCon 2019 in Santa Clara, I attended a couple of sessions where Cadence and their research partners provided some insight on machine learning/AI and on large system design analysis; with the first one focused on real-world cloud & machine learning/AI deployment for hardware design and the second one focused… Read More

Electronic Design Automation

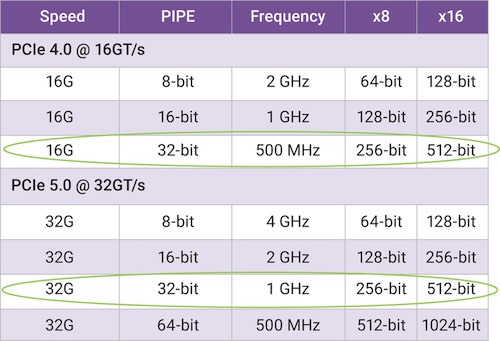

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

Mentor Showcases Digital Twin Demo

Mentor put on a very interesting tutorial at DVCon this year. Commonly DVCon tutorials center around a single tool; less commonly (in my recent experience) they will detail a solution flow but still within the confines of chip or chip + software design. It is rare indeed to see presentations on a full system design including realistic… Read More

Radar is Cheaper but Autonomous Car Needs Lidar!

To replace a human driver, autonomous car will have to “see” and do it in a better way than human being. The available solution, based on camera, radar, lidar, is not perfect and need to be improved. Radar is great for “seeing” in bad weather but has insufficient resolution to distinguish distant objects. Lidar produces high-resolution… Read More

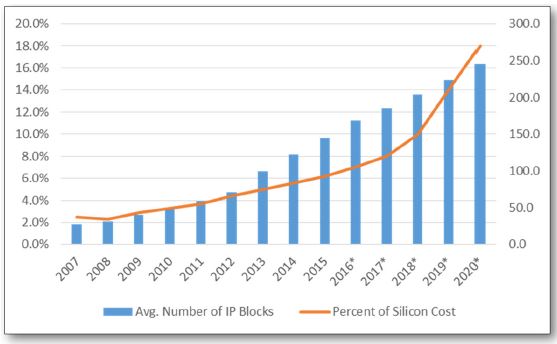

Synopsys GLOBALFOUNDRIES and Automotive IP

IP vendors have always had the inside track on the status of new process nodes and what customers are planning for their next designs. This is even more apparent now that systems companies are successfully doing their own chips by leveraging the massive amounts of commercial IP available today. Proving once again that IP really … Read More

How Well Did Methodics do in 2018?

In January I read from the ESDA Allianceabout EDA and Semiconductor IP revenues increasing 6.7% for Q3 2018, reaching $2,435.6 million, which is decent growth for our maturing industry. In stark contrast there’s a company called Methodicsthat specializes in Intellectual Property Lifecycle Management (IPLM) and traceability… Read More

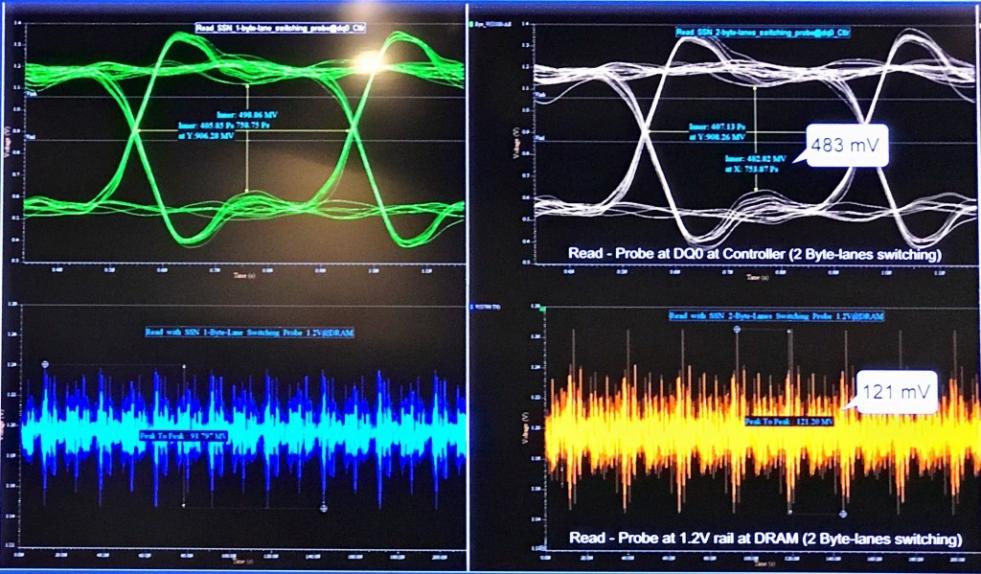

Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating … Read More

Delivering Innovation for Regulated Markets

When delivering devices to markets that require heavily audited compliance it is necessary to document and demonstrate development processes that follow the various standard(s) such as IEC65108, IATF16949, ISO26262.

For complex multi-disciplinary designs this can be difficult as they are often developed by multiple teams… Read More

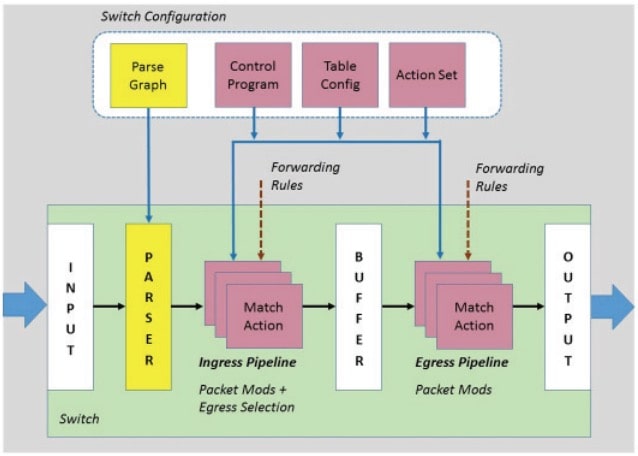

Verifying Software Defined Networking

I’ve designed hardware and written software for decades now, so it comes as no surprise to see industry trends like Software Defined Radio (SDR) and Software Defined Networking (SDN) growing in importance. Instead of designing a switch with fixed logic you can use an SDN approach to allow for greatest flexibility, even … Read More

Accelerating Post-Silicon Debug and Test

The recent growing complexity in SoC designs attributed to the increased use of embedded IP’s for more design functionalities, has imposed a pressing challenge to the post-silicon bring-up process and impacting the overall product time-to-market.

According to data from Semico Research, more than 60% of design starts contain… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center