The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More

Author: Mike Gianfagna

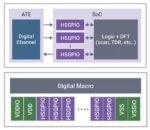

Synopsys Addresses the Test Barrier for Heterogeneous Integration

Infinisim Enables a Path to Greater Profitability and a Competitive Edge

Improved profitability and competitiveness are at the very heart of every enterprise. Achievements like this are usually attributed to corporate culture. Sometimes, it’s just being in the right place at the right time. Some organizations make huge investments with top-tier consulting companies to help find their way.

Recently… Read More

The Road to Innovation with Synopsys 224G PHY IP From Silicon to Scale: Synopsys 224G PHY Enables Next Gen Scaling Networks

The explosive growth of large language models (LLMs) has created substantial new requirements for chip-to-chip interconnects. These very large models are trained in high-performance data centers. Multiple accelerators need to work seamlessly to make all this possible as the bandwidth between accelerators directly impacts… Read More

Webinar – Achieving Seamless 1.6 Tbps Interoperability with Samtec and Synopsys

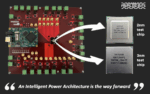

It is well-known that AI is upending conventional wisdom for system design. Workload-specific processor configurations are growing at an exponential rate. Along with this is an exponential growth in data bandwidth needs, creating an urgency for 1.6T Ethernet. A recent SemiWiki webinar dove into these issues. Synopsys and … Read More

How Arteris is Revolutionizing SoC Design with Smart NoC IP

Recently, Design & Reuse held its IP-SoC Days event at the Hyatt Regency in Santa Clara. Advanced IP drives a lot of the innovation we are seeing in chip design. This event provides a venue for IP providers to highlight the latest products and services and share a vision of the future. IP consumers are anxious to hear about all the… Read More

Analog Bits Steals the Show with Working IP on TSMC 3nm and 2nm and a New Design Strategy

The TSMC Technology Symposium recently kicked off in Santa Clara, with a series of events scheduled around the world. This event showcases the latest TSMC technology. It is also an opportunity for TSMC’s vast ecosystem to demonstrate commercial application on TSMC’s technology. There is a lot to unpack at an event like this. There… Read More

Silicon Creations Presents Architectures and IP for SoC Clocking

Design & Reuse recently held its IP-SoC Days event at the Hyatt Regency in Santa Clara. Advanced IP is now the fuel for a great deal of innovation in semiconductor design. This popular event allows IP providers to highlight the latest products and services and share a vision of the future. IP consumers can easily get updates on… Read More

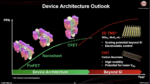

TSMC Describes Technology Innovation Beyond A14

The inaugural event for the 2025 TSMC Technology Symposium recently concluded in Santa Clara, California. This will be followed by events around the world over the next two months. We have summarized information from this event regarding process technology innovation and advanced packaging innovation. Overall, the A14 process… Read More

Siemens Describes its System-Level Prototyping and Planning Cockpit

We all know semiconductor design is getting harder. Much harder when you consider the demands of AI workloads and heterogeneous integration of many chiplets in a single package. This class of system demands co-optimization across the entire design flow. For example, functional verification, thermal analysis, signal and power… Read More

TSMC Brings Packaging Center Stage with Silicon

The worldwide TSMC 2025 Technology Symposium recently kicked off with the first event in Santa Clara, California. These events typically focus on TSMC’s process technology and vast ecosystem. These items were certainly a focus for this year’s event as well. But there is now an additional item that shares the spotlight – packaging… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center