The semiconductor ecosystem is changing. Monolithic design is becoming multi-die design. Processors no longer inform software development options. It’s now the other way around with complex AI software informing the design of purpose-built hardware. And all that special-purpose hardware needs drivers to make it come to … Read More

Author: Mike Gianfagna

Is Arteris Poised to Enable Next Generation System Design?

How Synopsys Enables Gen AI on the Edge

Artificial intelligence and machine learning have undergone incredible changes over the past decade or so. We’ve witnessed the rise of convolutional neural networks and recurrent neural networks. More recently, the rise of generative AI and transformers. At every step, accuracy has been improved as depicted in the graphic… Read More

Samtec Advances Multi-Channel SerDes Technology with Broadcom at DesignCon

There were many announcements and significant demonstrations of new technology at the recent DesignCon. The show celebrated its 30th anniversary this year and it has grown quite a bit. As in past years Samtec had a commanding presence at the show. There will be more about that in a moment, but first I want to focus on a substantial … Read More

Synopsys Expands Optical Interfaces at DesignCon

The exponential growth of cloud data centers is well-known. Driven by the demands of massive applications like generative AI, state-of-the-art data centers present substantial challenges in terms of power consumption. And AI is poised to drive a 160% increase in data center power demand while also increasing demands on storage… Read More

What is Different About Synopsys’ Comprehensive, Scalable Solution for Fast Heterogeneous Integration

Multi-die design has become the center of a lot of conversation lately. The ability to integrate multiple heterogeneous devices into a single package has changed the semiconductor landscape, permanently. This technology has opened a path for continued Moore’s Law scaling at the system level. What comes next will truly be exciting.… Read More

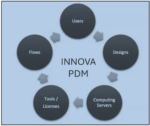

Webinar: Achieve Full Flow and Resource Management Visibility to Optimize Cost and Sustainability with Innova

The lifecycle for complex chip design includes many factors. Traditional systems focus on design tasks, associated schedules and manufacturing logistics. While these are important aspects of the project there is a lot more that can be measured, predicted and tracked. Taking a more holistic view of the project opens new opportunities… Read More

Synopsys Brings Embedded Memory to the Future with its Flexible, IP-Based Compilers

There is a revolution happening that is fueled by innovation in areas such as AI, IoT and autonomous driving. These new systems put incredible stress on next-generation semiconductor technology. Faster processing, higher density and lower latency must all be delivered with reduced power and thermal profiles. One technology… Read More

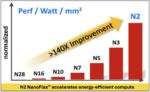

Intel Presents the Final Frontier of Transistor Architecture at IEDM

IEDM was buzzing with many presentations about the newest gate-all-around transistor. Both Intel and TSMC announced processes based on nanosheet technology. This significant process innovation allows the fabrication of silicon RibbonFET CMOS devices, which promise to open a new era of transistor scaling, keeping Moore’s… Read More

TSMC Unveils the World’s Most Advanced Logic Technology at IEDM

There was a lot of discussion at IEDM about the coming shift to gate-all-around (GAA) transistor structures. This new device brings many benefits to continue device scaling, both at the monolithic device level as well as for multi-die design. The path to GAA is not simple, there are new material, process and design considerations… Read More

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging Ahead

IEDM turned 70 last week. This was cause for much celebration in the form of special events. One such event was a special invited paper on Tuesday afternoon from Intel’s Tahir Ghani, or Mr. Transistor as he is known. Tahir has been driving innovation at Intel for a very long time. He is an eyewitness to the incredible impact of the Moore’s… Read More

Facing the Quantum Nature of EUV Lithography