We have a shortage of reference designs to test detection of security vulnerabilities. An LLM-based method demonstrates how to fix that problem with structured prompt engineering. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford,… Read More

Author: Bernard Murphy

Prompt Engineering for Security: Innovation in Verification

Siemens Proposes Unified Static and Formal Verification with AI

Given my SpyGlass background I always keep an eye out for new ideas that might be emerging in static and formal verification. Whatever can be covered through stimulus-free analysis reduces time that needn’t be wasted in dynamic analysis, also adding certainty to coverage across that range. Still, advances don’t come easily. … Read More

A Quick Look at Agentic/Generative AI in Software Engineering

Agentic methods are hot right now since single LLM models seem limited to point tool applications. Each such application is impressive but still a single step in the more complex chain of reasoning tasks we want to automate, where agentic methods should shine. I have been hearing that software engineering (SWE) teams are advancing… Read More

Insider Opinions on AI in EDA. Accellera Panel at DAC

In AI it is easy to be distracted by hype and miss the real advances in technology and adoption that are making a difference today. Accellera hosted a panel at DAC on just this topic, moderated by Daniel Nenni (Mr. SemiWiki). Panelists were: Chuck Alpert, Cadence’s AI Fellow driving cross-functional Agentic AI solutions throughout… Read More

ChipAgents Tackles Debug. This is Important

Innovation is never ending in verification, for performance, coverage, connection to verification plans and other aspects of DV. But debug, accounting for 40% of the verification cycle, has remained stubbornly resistant to significant automation. Debug IDEs help to visualize but don’t address the core problem: given a failure,… Read More

Reachability in Analog and AMS. Innovation in Verification

Can a combination of learning-based surrogate models plus reachability analysis provide first pass insight into extrema in circuit behavior more quickly than would be practical through Monte-Carlo analysis? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys… Read More

IP Surgery and the Redundant Logic Problem

It’s now difficult to remember when we didn’t reuse our own IP and didn’t have access to extensive catalogs of commercial IP. But reuse comes with a downside – without modification we can’t finetune IP specs to exactly what we want in a current design. We’re contractually limited in how we can adapt commercial IP, however vendors … Read More

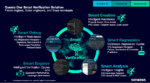

The Siemens Questa plus AI Story Gathers Momentum

I wrote recently about a Siemens pre-announcement at DVCon on their directions in simulation+AI. On May 13th they officially announced a full spectrum of capabilities under the brand Questa One. Abhi Kolpekwar (VP/GM at Siemens EDA) more fully fleshed out the story for me. I asked why Siemens is late to this simulation+AI party.… Read More

Arteris Expands Their Multi-Die Support

I am tracking the shift to multi-die design, so it’s good to see Arteris extend their NoC expertise, connecting chiplets across an interposer. After all, network connectivity needs don’t stop at the boundaries of chiplets. A multi-die package is at a logical level just a scaled-up SoC for which you still need traffic routing and… Read More

A Novel Approach to Future Proofing AI Hardware

There is a built-in challenge for edge AI intended for long time-in-service markets. Automotive applications are the obvious example, while aerospace and perhaps medical usage may impose similar demands. Support for the advanced AI methods we now expect – transformers, physical and agentic AI – is not feasible without dedicated… Read More

Things From Intel 10K That Make You Go …. Hmmmm