Dirk Didascalou, Siemens CTO, gave a keynote at DVCon, raising our perspective on why we do what we do. Yes, our work in semiconductor design enables the cloud and 5G and smart everything, but these technologies push progress for a select few. What about the big global concerns that affect us all: carbon, climate, COVID and conflict?… Read More

Author: Bernard Murphy

Intel Keynote on Formal a Mind-Stretcher

Synopsys has posted on the SolvNet site a fascinating talk given by Dr. Theo Drane of Intel Graphics. The topic is datapath equivalency checking. Might sound like just another Synopsys VC Formal DPV endorsement but you should watch it anyway. This is a mind-expanding discussion on the uses of and considerations in formal which … Read More

Accellera Update at DVCon 2023

I have a new-found respect for Lu Dai. He is a senior director of engineering at Qualcomm, with valuable insight into the ground realities of verification in a big semiconductor company. He is on the board of directors at RISC-V International and is chairman of the board of directors at Accellera, both giving him a top-down view of… Read More

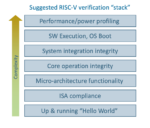

Scaling the RISC-V Verification Stack

The RISC-V open ISA premise was clearly a good bet. It’s taking off everywhere, however verification is still a challenge. As an alternative to Arm, the architecture and functionality from multiple IP providers looks very competitive, but how do RISC-V providers and users ensure the same level of confidence we have in Arm? Arm … Read More

Scaling AI as a Service Demands New Server Hardware

While I usually talk about AI inference on edge devices, for ADAS or the IoT, in this blog I want to talk about inference in the cloud or an on-premises datacenter (I’ll use “cloud” below as a shorthand to cover both possibilities). Inference throughput in the cloud is much higher today than at the edge. Think about support in financial… Read More

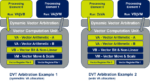

DSP Innovation Promises to Boost Virtual RAN Efficiency

5G is already real, though some of us are wondering why our phone connections aren’t faster. That perspective misses the real intent of 5G – to extend high throughput (and low latency) communication to a vast number and variety of edge devices beyond our phones. One notable application is Fixed Wireless Access (FWA), promising … Read More

Physically Aware NoC Design Arrives With a Big Claim

I wrote last month about physically aware NoC design, so you shouldn’t be surprised that Arteris is now offering exactly that capability 😊. First, a quick recap on why physical awareness is important, especially below 16nm. Today, between the top level and subsystems a state-of-art SoC may contain anywhere from five to twenty … Read More

ML-Based Coverage Acceleration. Innovation in Verification

We looked at another paper on ML-based coverage acceleration back in April 2022. Here is a different angle from IBM. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback… Read More

Synopsys Design Space Optimization Hits a Milestone

I talked recently with Stelios Diamantidis (Distinguished Architect, Head of Strategy, Autonomous Design Solutions) about Synopsys’ announcement on the 100th customer tapeout using their DSO.ai solution. My concern on AI-related articles is in avoiding the hype that surrounds AI in general, and conversely the skepticism… Read More

ASIL B Certification on an Industry-Class Root of Trust IP

I have always been curious about how Austemper-based safety methodologies (from Siemens EDA) compares with conventional safety flows. Siemens EDA together with Rambus recently released a white paper on getting a root of trust IP to ASIL B certification. This provides a revealing insight beyond the basics of fault simulation… Read More

Things From Intel 10K That Make You Go …. Hmmmm