Out of college my first job was doing circuit design at the transistor-level with Intel, and to get accurate SPICE netlists for simulation we had to manually count the squares of parasitic interconnect for diffusion, poly-silicon and metal layers. Talk about a burden and chance for mistakes, I’m so thankful that EDA companies have come to our rescue and have automated the extraction of parasitics that directly effect the quality of any digital or analog circuit performance in terms of speed, currents, power, IR drop and even reliability. If you were to just simulate your circuits without parasitic values, then the results are going to be quite a bit different from silicon, so it really makes sense to do SPICE simulations with extracted parasitic values in order to predict how silicon will behave.

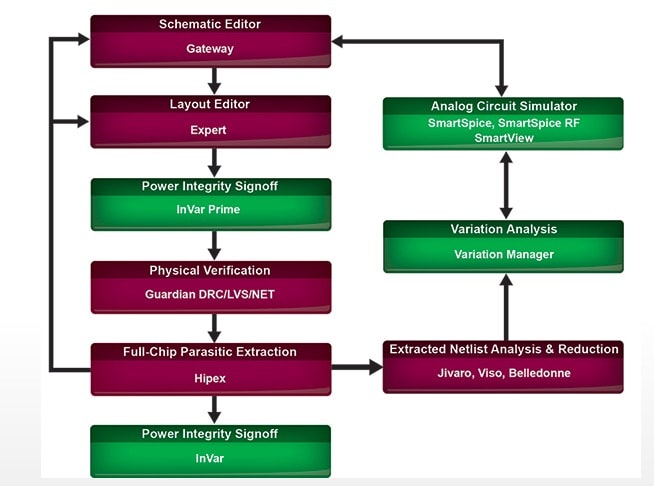

Silvaco is an EDA vendor with a growing list of tools for IC design as shown in this tool flow diagram:

To learn more about parasitic extraction from Silvaco you should consider attending their webinar on March 23rd from 10AM – 11AM PST. The three tools shown under Extracted Netlist Analysis & Reduction will also be discussed in the webinar. The presenter for the webinar is Jean-Pierre Goujon, an AE Manager based in France, and he previously worked at Edxact, a company acquired by Silvaco in June 2016.

If you do IC design with SPICE, or support CAD tools in a flow and work with PDKs, then this webinar is sure to answer your questions on what Silvaco has to offer. Registration for the webinar is here.

Parasitic extraction is a mandatory step for physical design sign off, and at advanced nodes, parasitics substantially impact the behavior of circuit design. Any analysis must consider the interconnect parasitic effects to produce meaningful and realistic results. In this webinar, we will review a flow that can qualitatively and quantitatively compare two extraction flavors for the same design. We will then present an in-depth exploration of exactly where the differences are coming from. At the end of this webinar, switching between different layout parasitic extraction tools, calibrating settings to a new technology node, qualifying PDK updates etc will no longer be a bottleneck for CAD teams.

What attendees will learn:

- Powerful and accurate methods to qualify and quantify different parasitic extraction methods

- How to recognize traps in the flow and possible work-arounds

- How to explore parasitics and analyze what is different and where

PRESENTER:

Mr. Jean-Pierre Goujon is Application Manager for Silvaco France. He is responsible for customer technical support for EDA products, with a specific interest in parasitic analysis and reduction products. Prior to this position, he has been AE manager for Edxact for 12 years and had various AE responsibilities at Cadence, Simplex and Snaketech mostly in the field of parasitic extraction.

Mr. Goujon holds a BSc in EEE from Robert Gordon University, Aberdeen, UK and a MS in EEE from Ecole Supérieure de Chimie, Physique, Electronique de Lyon, France.

Related Blogs

- It’s Time to Put Your SPICE Netlist on a Diet

- Custom IC Design Flow with OpenAccess

- IC Design and OpenAccess

- Variation Aware FinFETs are Critical!

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.