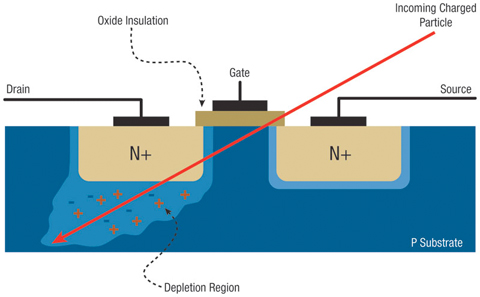

Do you know what a SEE is? It stands for single event upset. We live on a radioactive planet which is also bombarded with cosmic rays, so particles are bombarding our chips. The materials used in packaging also can create particles that cause problems, even the solder. Reliability and aging has been an area that has not been at the forefront of people’s minds while the huge volumes in leading edge processes are mostly driven by the smartphone market. If your phone crashes or reboots it is not the end of the world. But as medical, automotive and aerospace start moving into more advanced nodes we will certainly care. If the ABS system in your car crashes you certainly care a lot. And even in communications, while our cellphones are not a big deal, large enterprise routers crashing upsets their owners, so it is not just an issue for the life-critical systems.

Do you know what a SEE is? It stands for single event upset. We live on a radioactive planet which is also bombarded with cosmic rays, so particles are bombarding our chips. The materials used in packaging also can create particles that cause problems, even the solder. Reliability and aging has been an area that has not been at the forefront of people’s minds while the huge volumes in leading edge processes are mostly driven by the smartphone market. If your phone crashes or reboots it is not the end of the world. But as medical, automotive and aerospace start moving into more advanced nodes we will certainly care. If the ABS system in your car crashes you certainly care a lot. And even in communications, while our cellphones are not a big deal, large enterprise routers crashing upsets their owners, so it is not just an issue for the life-critical systems.

Addressing SEE has to be done at several levels. Materials, the process, the design of cell libraries, the design itself at the SoC level. This is one of the areas that you are going to have to worry more about in the future since, like pretty much anything to do with semiconductors, the problem gets worse with each process node. The transistors are smaller and easier to flip. Memory bits are smaller and easier for a particle to cause a multi-bit upset. Analysis requires tools at the TCAD level and also at the standard design level.

Silvaco has a webinar coming up soon to go over all the issues as to how to analyze your design. The webinar will provide a discussion of the methods used by radiation effects engineers to model the impact of Single Event Effects (SEE) and some of their effects on devices and circuits. The remarkable advances in modern device technology creates specific challenges for high–fidelity radiation effects modeling of these phenomena, while the reduction of feature sizes has made the accurate modeling of SEE and other radiation effects of critical importance. These include the need for modeling Soft Error Rates (SER), Multi Bit Upsets (MBU), chip packaging, and detailed single event effects modeling at the device and circuit level.

The agenda for the webinar is:

- Why understanding SEE is important

- Basic mechanisms

- Destructive single events effects

- Modeling and analysis –TCAD tool flow

- Device techniques for increasing resiliency to SEE

- Non-Destructive single event effects

- Modeling and analysis –TCAD and EDA tool flow

- Device and circuit techniques for reducing non–destructive SEE

- System methodology examples for a DC-DC boost converter, power diode, and logic block with quenching

The webinar Modeling and Analysis of Single Event Upsetswill be presented by Dr. Christopher Nicklaw, Staff Scientist at Silvaco, who has over thirty-five (35) years experience working on radiation effects in materials. It is Tuesday July 8th from 10am to 11am Pacific Time.

More details are here. Even if you can’t make that time, register anyway and Silvaco will email you a link to the on-demand webinar afterwards.

More articles by Paul McLellan…

Share this post via:

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

0 Replies to “Single Event Upsets”

You must register or log in to view/post comments.