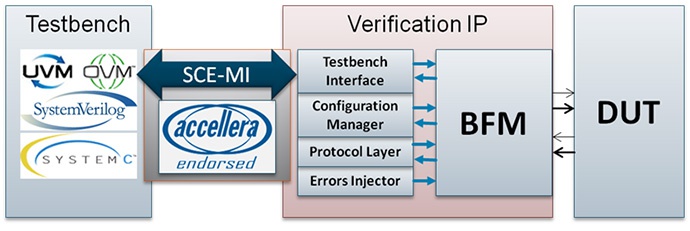

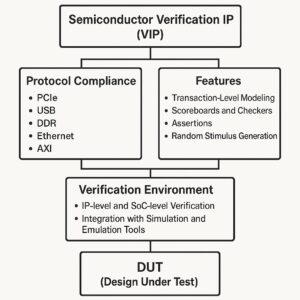

Semiconductor Verification IP (VIP) is a pre-verified, reusable block of code or models used in simulation and verification environments to validate the correctness and interoperability of semiconductor designs. VIPs emulate the behavior of industry-standard protocols, interfaces, or system components, allowing verification engineers to test the functionality, compliance, and performance of their SoCs (System-on-Chips), ASICs (Application-Specific Integrated Circuits), or FPGAs.

Purpose and Importance:

Verification is one of the most resource-intensive and time-consuming aspects of chip development, often consuming over 70% of the total design cycle. As modern SoCs integrate dozens or even hundreds of IP blocks, interfaces, and subsystems, verifying that all these components work correctly together is critical.

Verification IP addresses this by:

-

Emulating real-world protocol behavior.

-

Automating stimulus generation and response checking.

-

Enabling early system-level validation.

-

Accelerating time-to-market by reducing testbench development time.

Typical Features of VIP:

-

Protocol Compliance: Models for standards like PCIe, USB, DDR, Ethernet, AXI, AMBA, etc.

-

Transaction-Level Modeling (TLM): Speeds up simulation and integration.

-

Scoreboards and Checkers: Automated response validation and coverage analysis.

-

Assertions: Formal or simulation-based checks for corner cases.

-

Random Stimulus Generation: Enables functional coverage and corner-case testing.

-

Integration with Simulation and Emulation Tools: Works with tools like Synopsys VCS, Cadence Xcelium, Siemens Questa, etc.

-

Debug Features: Including protocol-aware debug, waveform visualization, and coverage metrics.

Common Protocols with Available VIP:

| Protocol | Application |

|---|---|

| PCI Express (PCIe) | High-speed IO and connectivity |

| DDR / LPDDR / HBM | Memory interfaces |

| Ethernet | Networking and data communication |

| USB | Consumer electronics and host-device communication |

| MIPI CSI/DSI | Imaging and display in mobile and automotive |

| AXI / AHB / APB (AMBA) | On-chip bus communication |

| I2C / SPI | Low-speed serial communication |

| UCIe | Chiplet interconnect verification |

VIP Usage in the Design Flow:

-

IP-Level Verification: Validate functional correctness of individual blocks.

-

Subsystem Verification: Integrate and verify interactions across multiple blocks.

-

SoC Verification: System-level verification across multiple domains and interfaces.

-

Emulation/Prototyping: Use VIPs with Palladium (Cadence), Veloce (Siemens), or ZeBu (Synopsys) to accelerate software validation and HW/SW co-design.

Major VIP Vendors:

| Vendor | VIP Products |

|---|---|

| Synopsys | VC Verification IP, Verdi Protocol Analyzer |

| Cadence | VIP Catalog (e.g., PCIe, USB), Memory Models, System VIP |

| Siemens EDA (formerly Mentor) | Questa VIP, Verification Academy resources |

| Avery Design Systems | Extensive third-party VIP portfolio for memory, PCIe, USB, etc. |

| SmartDV | Broad protocol coverage, customizable VIP solutions |

| Truechip | Cost-effective VIP offerings for popular protocols |

| EDA Playground/VIP Central | Open-access VIP learning platforms |

Trends and Innovations:

-

VIP for Chiplets: New VIPs for UCIe, die-to-die links, and heterogeneous integration.

-

AI/ML in Verification: Smart coverage analysis and debug using ML techniques.

-

Formal VIP: Formal verification libraries used for exhaustive corner-case analysis.

-

Portable Stimulus Standards (PSS): Portable test scenarios using PSS (from Accellera).

-

Accelerated VIP: Optimized for hardware-assisted verification and hybrid flows.

Challenges in Using VIP:

-

Integration Complexity: Matching VIP configurations with DUT can be non-trivial.

-

Performance Bottlenecks: Simulation speed can slow down due to complex protocols.

-

Maintenance and Updates: Keeping VIP compliant with evolving protocol specs.

-

Debug and Learning Curve: Steep learning curve for advanced features.

Applications Across Industries:

-

Consumer Electronics: USB, HDMI, MIPI-based designs.

-

Automotive SoCs: Ethernet AVB/TSN, CAN, MIPI, and memory VIPs.

-

Data Center and HPC: PCIe Gen5/6, CXL, DDR5, HBM VIPs.

-

Mobile and AI SoCs: UFS, LPDDR, AXI interconnect VIPs.

-

Aerospace and Defense: Specialized secure protocol VIPs (e.g., SpaceWire).

Future Outlook:

As SoCs grow in complexity and include multiple domains (AI/ML, security, analog/mixed-signal, chiplets), the role of VIP is expanding beyond just protocol compliance into system-level modeling, debug, and predictive verification using AI. VIP will also play a pivotal role in pre-silicon software development and virtual platform creation.

Things From Intel 10K That Make You Go …. Hmmmm