Overview

A Digital Signal Processor (DSP) is a specialized microprocessor or IP core optimized for real-time numerical computation, particularly for tasks involving digital signal processing—such as filtering, audio/video encoding, communications, radar, and image recognition.

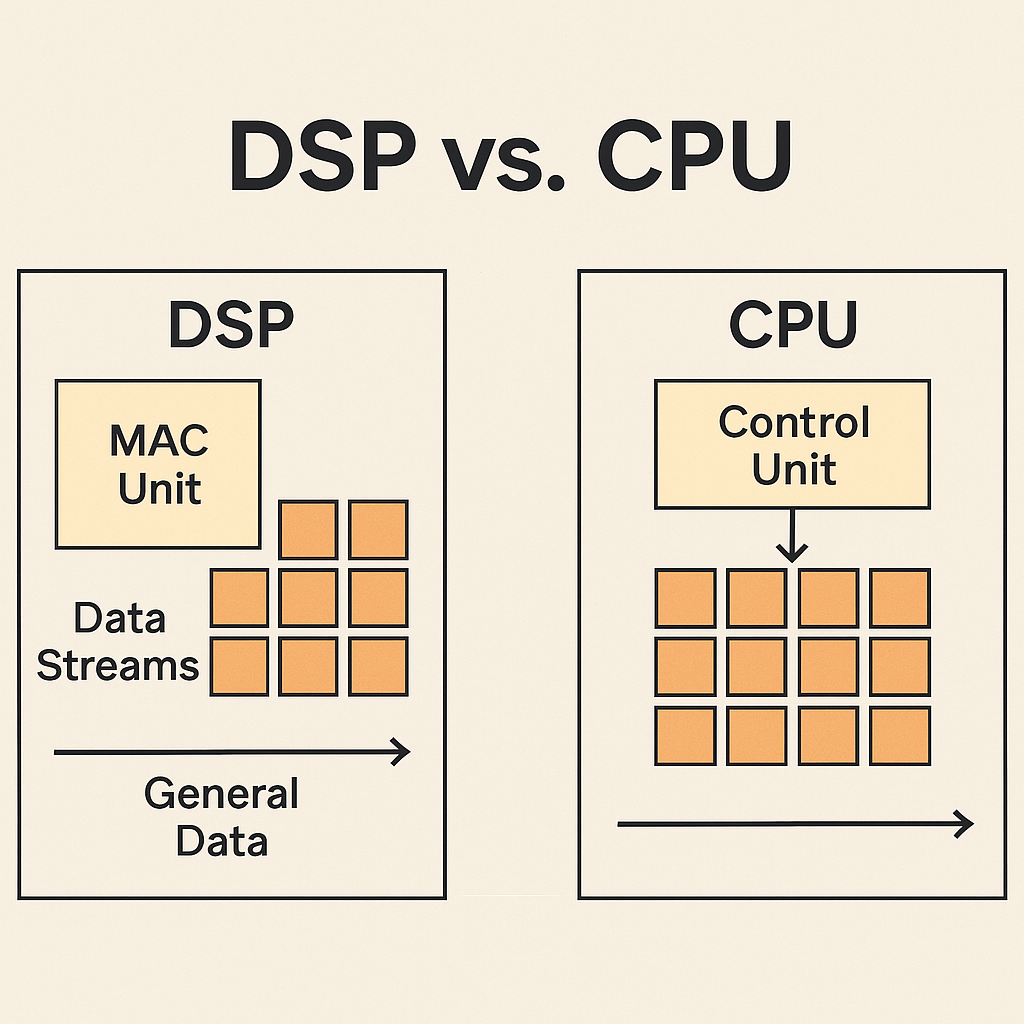

DSPs are designed to handle streaming data, applying fast and efficient mathematical operations (especially multiply-accumulate, or MAC) on continuous real-time input. They are essential for embedded systems, IoT devices, consumer electronics, automotive, and AI/ML inference at the edge.

🧠 Core Characteristics

| Feature | Description |

|---|---|

| MAC Unit (Multiply-Accumulate) | Enables fast dot products and filtering operations |

| Fixed-Point or Floating-Point Support | Optimized for high-precision or energy-efficient computation |

| Zero-Overhead Loops | Supports repeated operations without performance penalty |

| Harvard Architecture | Separate data and instruction buses for higher throughput |

| SIMD (Single Instruction, Multiple Data) | Executes parallel operations on vectors |

| Low Power Design | Tailored for embedded and portable applications |

🛠️ DSP Applications

| Domain | Examples |

|---|---|

| Audio Processing | MP3 codecs, echo cancellation, digital hearing aids |

| Image and Video | Compression (JPEG, MPEG, H.264), image enhancement |

| Telecom | OFDM modulation, equalizers, channel coding |

| Radar & Sonar | Signal filtering, pulse compression |

| Medical Devices | ECG signal analysis, ultrasound |

| Automotive | Lidar/ultrasound processing, noise suppression |

| Edge AI/ML | Inference acceleration using MACs, sparse matrix ops |

🧱 DSP vs. General-Purpose Processor (GPP)

| Feature | DSP | GPP |

|---|---|---|

| Data Type | Streams of samples | General data |

| MAC Unit | Yes (dedicated) | No or slower |

| Instruction Set | Signal-optimized | General-purpose |

| Latency | Low, deterministic | Variable |

| Use Case | Real-time processing | Broad computing tasks |

💡 DSP Implementations

1. Standalone DSP Chips

-

Used in legacy or ultra-low power systems

-

Examples: TI TMS320 series, Analog Devices Blackfin

2. DSP IP Cores

-

Embedded in SoCs and FPGAs

-

Examples:

-

Cadence Tensilica HiFi DSP (audio/voice)

-

CEVA DSP cores (wireless, vision, AI)

-

Synopsys ARC HS DSP

-

Arm Helium (M-Profile Vector Extension) for Cortex-M

-

3. DSP Blocks in FPGAs

-

Xilinx (AMD) and Intel (Altera) FPGAs include hardened DSP slices for MACs

🧰 Key Features in DSP Toolchains

-

Fixed-Point and Floating-Point Libraries

-

Real-Time Operating Systems (RTOS)

-

Vector and DSP compiler optimizations

-

MATLAB/Simulink integration for modeling

-

DSP assembly languages for fine-tuned performance

🔁 DSP Architectures

| Architecture | Use |

|---|---|

| VLIW (Very Long Instruction Word) | Parallel execution of multiple ops per cycle |

| SIMD (Vector DSP) | Efficient processing of data arrays |

| Dual-Harvard Architecture | Separate buses for instruction/data/code |

| Tightly Coupled Memory (TCM) | Low-latency data access in real-time loops |

🔌 DSP in AI & Machine Learning

Modern DSPs are evolving to support AI inference workloads:

-

Optimized for matrix multiplication, convolution, and sparse data

-

Used in edge AI for voice recognition, keyword spotting, sensor fusion

-

DSP-based NPUs (neural processing units) leverage vector extensions and AI-specific instructions

🏢 Key DSP Companies

| Vendor | Specialty |

|---|---|

| Texas Instruments (TI) | Legacy DSP processors (TMS320, C6000) |

| Analog Devices (ADI) | Blackfin, SHARC audio DSPs |

| Cadence Tensilica | HiFi audio DSPs, Vision P DSPs |

| CEVA | Wireless, imaging, AI DSP cores |

| Synopsys ARC | Embedded DSP and control processors |

| Arm | Cortex-M with Helium vector DSP extensions |

| Qualcomm Hexagon | Integrated DSPs in Snapdragon SoCs |

📈 Market Trends

| Trend | Description |

|---|---|

| Edge AI Acceleration | DSPs used as low-power AI coprocessors |

| Audio and Voice DSP Growth | In smart speakers, wearables, hearing aids |

| DSP-IP in Custom SoCs | RISC-V SoCs often integrate open DSP extensions |

| Software-Defined Radio (SDR) | DSPs enable programmable baseband processing |

| Neural DSPs (NDSPs) | Hybrids for mixed AI+signal workloads |

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry