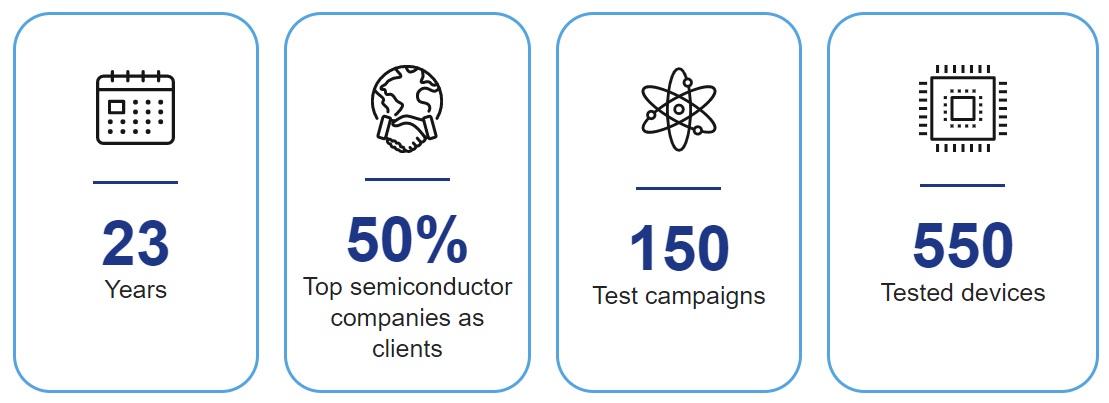

IROC Technologies specializes in helping the semiconductor industry to evaluate and manage reliability risks throughout the chip design and manufacturing process. As deep submicron technology makes chips more vulnerable to component and system reliability issues, IROC provides analysis software, test services, and expert consultation to reduce risks and improve chip quality.

More than half of our executives have been working at IROC for at least 10 years, working toward a more reliable SoC with respect to radiation impacts. We work collaboratively to reach our intrinsic goal to meet the needs and satisfaction of our customers and stakeholders.

PRODUCTS

TFIT

Best-in-class cell level soft error detector

Comments

There are no comments yet.

You must register or log in to view/post comments.