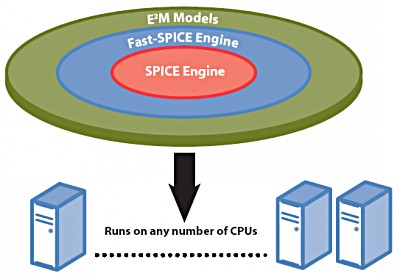

All four of the public EDA companies offer SPICE circuit simulation tools for use by IC designers at the transistor-level, and Magma has been offering two SPICE circuit simulators:

- FineSIM SPICE (parallel SPICE)

- FineSIM PRO (accelerated, parallel SPICE)

An early advantage offered by Magma was a SPICE simulator that could be run in parallel on multiple CPUs. The SPICE competitors have all now followed suit and re-written their tools to catch up to FineSim in that feature.

I also blogged about FineSIM SPICE and FineSIM Pro in June at DAC.

When I talk to circuit designers about SPICE tools they tell me that they want:

- Accuracy

- Speed

- Capacity

- Compatibility

- Integration

- Value for the dollar

- Support

The priority of these seven attributes really depends on what you are designing.

Feedback from anonymous SPICE circuit benchmarks concludes that FineSim SPICE can be preferred versus Synopsys HSPICE:

- Accuracy – about the same, qualified at TSMC for 65nm, 40nm and 28nm

- Speed – FineSim SPICE can be 3X to 10X faster

- Capacity – around 1.5M MOS devices, up to 30M RC elements

- Compatibility – uses inputs: HSPICE, Spectre, Eldo, SPF, DSPF. Models: BSIM3, BSIM4. Outputs: TR0, fsdb, WDF.

- Integration – co-simulates with Verilog, Verilog-A and VHDL

- Value – depends on the deal you can make with your Account Manager

- Support – excellent

Room for Improvement

Cadence, Synposys and Mentor all have HDL simulators that support: Verilog, VHDL, System Verilog and System C. These HDL simulators have been deeply integrated with their SPICE tools, letting you simulate accurate analog with the SPICE engine in context with Digital. Magma has no Verilog or VHDL simulator and only does a co-simulation, which is really primitive in comparison to these deeper integrations using single kernel technology.

Memory designers use hierarchy and FineSim Pro does offer a decent simulation capacity of 5M MOS devices, although it is not a hierarchical simulator so you cannot simulate a hierarchical netlist with 100M or more transistors in it. Both Cadence and Synopsys offer hierarchical SPICE simulators. With FineSim Pro you have to adopt a methodology of netlist cutting to simulate just the critical portions of your hierarchal memory design.

Summary

You really have to benchmark a SPICE circuit simulator on your own designs, your models, your analysis, and your design methodology to determine if it is better than what you are currently using. This is a highly competitive area for EDA tools and by all accounts Magma has world-class technology that works well for a wide range of transistor-level netlists, like: custom analog IP, large mixed-signal designs, memory design and characterization.

We’ve setup a Wiki page for all SPICE and Fast SPICE circuit simulatorsto give you a feel for which companies have tools.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era