Intro

I met with CK Lee, founder of Cyber EDA at his booth on Monday evening in San Diego. Last year I learned about their new SPICE circuit simulator named PCSIM, this year the new product is called ADDS-Debugger.

Notes

2010 – Announced a debugger

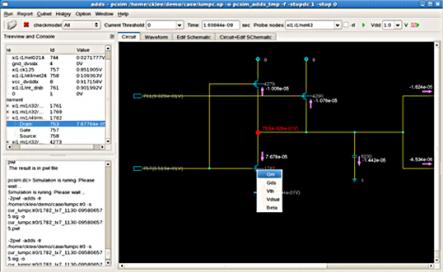

2011 ADDS Debugger – trace at the transistor level your design

– Signal tracing

– Post-layout debug

o Tracing – which signal triggered that net that rose or fall?

o Trace back to a Primary input

o Cross-probe between auto-generated Schematic and the waveforms

o Pricing: $50K per year

– ADDS Wave

o Pricing: $2K per year

– PCSim

o Pricing: $25K per year

o Post-layout simulation speed improved, 3X

o True SPICE simulator, flattened

o Compete with HSPICE, SPectre, ELdo

Customers – Ali (Taiwan)

– Extreme DA

Based: Santa Clara, CA

Employees: 10

Next Year: Double revenues

Sales: Direct mostly, some distributors

Summary

ADDS Debugger reminded me a lot of what Concept Engineering has been offering for several years now in a transistor-level debugger. What makes this different is that you’re inside of a circuit simulation run when you can visualize the netlist as a schematic and see the node voltages and branch currents.

The SPICE circuit simulator market is crowded with many EDA vendors (Synopsys, Mentor, Cadence, Magma, Berkeley, Tanner EDA), so Cyber EDA has to do something special in order to make PCSIM stand out from the crowd (speed, accuracy, capacity, features).

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era