As the complexity of modern System-on-Chip (SoC) designs continues to rise, achieving energy efficiency measured as performance per watt has become a crucial design goal. With the increasing demand for powerful, multifunctional chips, balancing performance with power consumption has become essential. Realistic workloads… Read More

Tag: webinar

Webinar: Fast and Accurate High-Sigma Analysis with Worst-Case Points

IC designers are tasked with meeting specifications like robustness in SRAM bit cells where the probability of a violation are lower than 1 part-per-billion (1 ppb). Another example of robustness is a Flip-Flop register that must have a probability of specification violation lower than 1 part-per-million (1 ppm). Using Monte… Read More

WEBINAR: An Ideal Neural Processing Engine for Always-sensing Deployments

Always-sensing cameras are a relatively new method for users to interact with their smartphones, home appliances, and other consumer devices. Like always-listening audio-based Siri and Alexa, always-sensing cameras enable a seamless, more natural user experience. However, always-sensing camera subsystems require specialized… Read More

MIPI bridging DSI-2 and CSI-2 Interfaces with an FPGA

We’re so spoiled by 4K and 8K and frame rates of 120 Hz or higher video content on high-performance devices that now, many of us expect these higher resolutions and rates on even small devices. The necessary interfaces exist in MIPI Display Serial Interface 2 (DSI-2) and Camera Serial Interface 2 (CSI-2). The challenge is these interfaces… Read More

WEBINAR: Flash Memory as a Root of Trust

It should not come as a surprise that the vast majority of IoT devices are insecure. As an indication, one survey estimates that 98% of IoT traffic is unencrypted. It’s not hard to understand why. Many such devices are cost-sensitive, designing security into a product is hard, buyers aren’t prepared to pay a premium for security … Read More

WEBINAR: O-RAN Fronthaul Transport Security using MACsec

5G provides a range of improvements compared to existing 4G LTE mobile networks in regards to capacity, speed, latency and security. One of the main improvements is in the 5G RAN; it is based on a virtualized architecture where functions can be centralized close to the 5G core for economy or distributed as close to the edge as possible… Read More

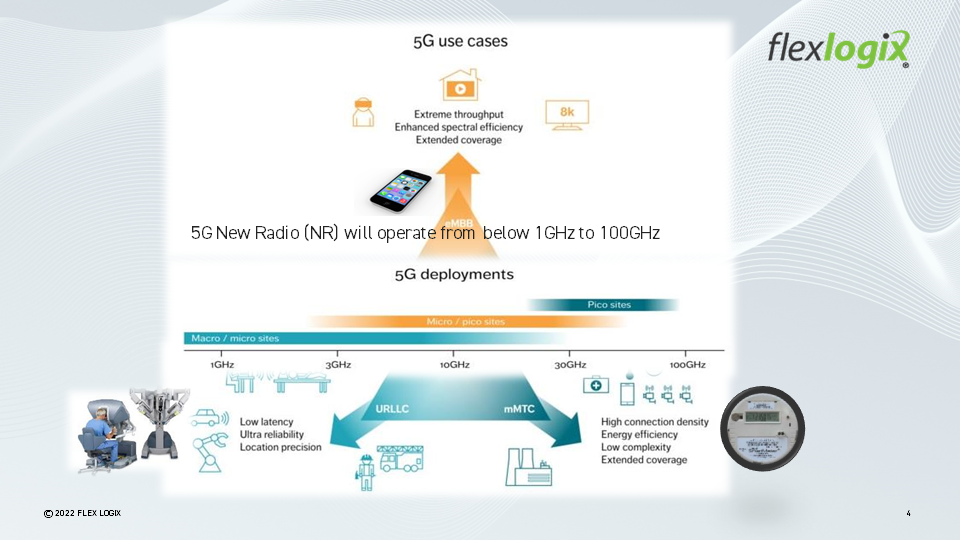

WEBINAR: 5G is moving to a new and Open Platform O-RAN or Open Radio Access Network

The demands of 5G requires new designs to not only save power but also increase performance and by moving to advance power-saving nodes and by using eFPGAs will help to achieve these goals. This paper will introduce 5G and O-RAN, the complexity of these systems, and how flexibility could be beneficial. Then we will dive into how eFPGA… Read More

Webinar – 112 Gbps PAM4 Implementation with Real-World Case Studies

Are 112G PAM4 channels in one of your current or future designs? If you’re focusing on advanced products, the answer is likely YES. Design of these channels is quite challenging. Silicon design, SerDes, PCB traces, and interconnect all need to be balanced to achieve success. As they say, getting there is half the fun. An upcoming… Read More

Webinar: AMS, RF and Digital Full Custom IC Designs need Circuit Sizing

My career started out by designing DRAM circuits at Intel, and we manually sized every transistor in the entire design to get the optimum performance, power and area. Yes, it was time consuming, required lots of SPICE iterations and was a bit error prone. Thank goodness times have changed, and circuit designers can work smarter … Read More

Webinar on Dealing with the Pain Points of AI/ML Hardware

Ever increasing data handling demands make creating hardware for many applications extremely difficult. In an upcoming webinar Achronix, a leading supplier of FPGA’s, talks about the data handling requirements for AI/ML applications – which are growing at perhaps one of the highest rates of all. Just looking at all data… Read More