In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

Tag: variation

Solido Wrote the Book on Variation

When I studied mathematical analysis, one of the things that we had to prove turns out to be surprisingly difficult. If you have a continuous function and at one point it is below a line (say zero) and at another point it is above zero, then there must be a point at which the value is exactly zero. In effect, a continuous function can’t… Read More

Designing for Variation

There is a widespread phenomenon in designing chips that new effects creep up on you. First they are so small you can ignore them. Then you can add a little pessimism to your timing budget or whatever gets affected. But eventually the effects go from second order to first order. You certainly can’t ignore them, and the guard … Read More

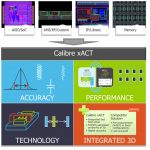

Calibre xACT Shakes Up 16nm and Below Extraction Game

Mentor Graphics made a big announcement regarding SOC extraction at their User2User conference in San Jose during April. Before I get to the meat of the announcement, I’d like to reflect back on the early days of Calibre-DRC at Mentor. I was in Sales at Mentor around 1999, and Calibre-DRC was the new kid on the block. We had to go convince… Read More

Variation Alphabet Soup

On-chip variation (OCV) is a major issue in timing signoff, especially at low voltages or in 20/16/14nm processes. For example, the graph below shows a 20nm inverter. At 0.6V the inverter has a delay of 2 (nominalized) units. But due to on-chip variation this might be as low as 1.5 units or as high as 3 units, which is a difference from… Read More

Voltage Limbo Dancing: How Low Can You Go?

All chips these days have to worry about power. Indeed it is typically the top of the priority list of concerns, above performance and even area. Transistors are effectively fast and free, but you can’t have too many of them (at least turned on at once). The most obvious way to reduce power is to lower the supply voltage. This … Read More

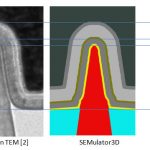

Coventor Panel at IEDM Digs into Variation Issues

Recently I attended a panel discussion on variability in semiconductor fabrication hosted by Coventor in conjunction with the IEEE IEDM conference in San Francisco. The IEEE bills the conference as “the world’s pre-eminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device… Read More

Variation: How Can We Survive?

At IEDM last week Coventor hosted a panel session as they do each year. The theme this year was surviving variation. The panel was hosted by someone whose name is familiar round here, Dan Nenni. The panel that Coventor had put together had people from all sorts of different slots in the design/supply chain for semiconductor. Unfortunately… Read More

Variation at IEDM

IEDM (technically the International Electron Devices Meeting although I’ve never heard anyone use the full name) is in a couple of weeks time, in San Francisco. It is December 15-17th at the Hilton Union Square (which is not actually at Union Square but nearby at 333 O’Farrell Street).

For the last few years on the Tuesday… Read More

Five Things You Don’t Know About MunEDA

So first the one thing that you do know. MunEDA are based in Munich which makes them German. I have to confess that until I got involved helping them a bit with some marketing stuff that that was about all I knew about them too.

So now five things that you might not know:

1. MunEDA have a much wider customer list that you know and would even… Read More