Today Alchip Technologies, a Taipei-based leader in high-performance and AI computing ASICs, announced a significant milestone with the successful tape-out of its 3D IC test chip. This achievement not only validates Alchip’s advanced 3D IC ecosystem but also positions the company as a frontrunner in the rapidly evolving field… Read More

Tag: UCIe

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Revolutionizing Chip Packaging: The Impact of Intel’s Embedded Multi-Die Interconnect Bridge (EMIB)

In an era dominated by artificial intelligence (AI), machine learning (ML), and high-performance computing (HPC), the demand for semiconductors that deliver high data throughput, low latency, and energy efficiency has never been greater. Traditional chip designs often struggle to keep pace with these requirements, leading… Read More

Streamlining Functional Verification for Multi-Die and Chiplet Designs

As multi-die and chiplet-based system designs become more prevalent in advanced electronics, much of the focus has been on physical design challenges. However, verification—particularly functional correctness and interoperability of inter-die connections—is just as critical. Interfaces such as UCIe or custom interconnects… Read More

UCIe 3.0: Doubling Bandwidth and Deepening Manageability for the Chiplet Era

cHBM for AI: Capabilities, Challenges, and Opportunities

AI’s exponential growth is transforming semiconductor design—and memory is now as critical as compute. Multi-die architecture has emerged as the new frontier, and custom High Bandwidth Memory (cHBM) is fast becoming a cornerstone in this evolution. In a panel session at the Synopsys Executive Forum, leaders from AWS, Marvell,… Read More

Alphawave Semi and the AI Era: A Technology Leadership Overview

The explosion of artificial intelligence (AI) is transforming the data center landscape, pushing the boundaries of compute, connectivity, and memory technologies. The exponential growth in AI workloads—training large language models (LLMs), deploying real-time inference, and scaling distributed applications—has … Read More

Intel’s Path to Technological Leadership: Transforming Foundry Services and Embracing AI

Intel, long a leader in semiconductor manufacturing, is on a determined journey to reclaim its technological leadership in the industry. After facing significant challenges in recent years, the company is making a concerted effort to adapt and innovate, with a clear focus on AI-driven technologies, advanced packaging solutions,… Read More

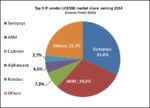

Design IP Market Increased by All-time-high: 20% in 2024!

Design IP revenues achieved $8.5B in 2024 and this is an all-time-high growth of 20%. Wired Interface is still driving Design IP growth with 23.5% but we see the Processor category also growing by 22.4% in 2024. This is consistent with the Top 4 IP companies made of ARM (mostly focused on processor) and a team leading wired interface… Read More

A Synopsys Webinar Detailing IP Requirements for Advanced AI Chips

Generative AI is dramatically changing the compute power that must be delivered by advanced designs. This demand has risen by more than 10,000 times in the past five to six years. This increased demand has impacted the entire SoC design flow. We are now faced with going beyond 1 trillion transistors per chip, and systems now consist… Read More