You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I had a meeting with Harn Hua Ng, the CEO of Plunify, a couple of weeks ago. They are an EDA company that I’d never heard of. Partially that is because they only play in the FPGA space, a country I visit less frequently than SoC land. Plus, they are based in Singapore, a country I have only been to a couple of times in my life.

Plunify… Read More

We’ve all heard this claim: “Our FPGA synthesis tool produces better quality of results (QoR).” If you’re just hoping for a tool to do that automagically, you’re probably doing it wrong. Getting better QoR depends on understanding what an FPGA synthesis tool is capable of, and how to leverage what it tells you.… Read More

I recently published a post on LinkedIn titled “Sometimes, you gotta throw it all out” in reference to the innovation process and getting beyond good to better. A prime example has crossed my desk: the new ProtoCompiler software for Synopsys HAPS FPGA-based prototyping systems.

Last week, I spoke with Troy Scott, product marketing… Read More

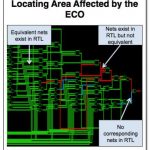

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More

Today Cadence announced Tempus, their new timing signoff solution. This has been in development for at least a couple of years and has been built from the ground up to be massively parallelized. Not just that different corners can be run in parallel (which is basically straightforward) but that large designs can be partitioned … Read More

There’s a nice article on timing closure by Dr. Jason Xing, Vice President of Engineering at ICScape Inc. on the Chip Design website. Not familiar with ICScape? Paul McLellan called ICScape the The Biggest EDA Company You’ve Never Heard Ofand Daniel Payne did Schematic, IC Layout, Clock and Timing Closure from ICScape at… Read More