At the DAC show in June I met with folks at Berkeley DA and heard about their Analog Fast SPICE simulator being used inside of the Tanner EDA tools. With the newest release from Tanner called HiPer Silicon version 15.23 you get a tight integration between:… Read More

Tag: tanner eda

SpringSoft Laker vs Tanner EDA L-Edit

Daniel Payne recently blogged some of the integration challenges facing Synopsys with their impending acquisition of SpringSoft. On my way back from San Diego last week I stopped by Tanner EDA to discuss an alternative tool flow for users who find themselves concerned about the Laker Custom Layout road map.

Design of the analog… Read More

IC Design at Novocell Semiconductor

In my circuit design past I did DRAM work at Intel, so I was interested in learning more about Novocell Semiconductor and their design of One Time Programmable (OTP) IP. Walter Novosell is the President/CTO of Novocell and talked with me by phone on Thursday.… Read More

Designing a Wafer-Scale Image Sensor for use in X-Rays

At Intel we mused about designing wafer-scale integration (WSI) back in the 70’s however I just learned about how Dr.Renato Turchetta at the Science and Technology Facilities Council (STFC) designed a wafer-scale imaging sensor chip for X-Ray applications. I was also able to interview Dr. Turchetta to learn more about… Read More

Tanner EDA Update 2012

Rather than fly to Southern California this week I decided to drive. Airport parking and security, flying to Irvine and renting a car, driving to San Diego and back to Irvine, then flying home is just too much. Call it Porsche therapy, I would rather drive. On the way home I will take the scenic 101 and enjoy the ocean views.

First stop… Read More

Analog FastSPICE added to Tanner EDA

Last year when I visited Tanner EDA at DAC I heard about how they integrated the Analog FastSPICE circuit simulator from Berkeley DA.

This made sense to me because BDA has a good reputation for speeding up SPICE without compromising on accuracy, and Tanner users may want to mix and match tools from multiple EDA vendors.

This year they’ve… Read More

Aldec and Tanner EDA at DAC

In April I blogged about a webinar on co-simulation hosted by Aldec and Tanner EDA where they showed how the RTL simulator (Riviera PRO) and SPICE simulator (T-Spice) had been connected together for IC designers wanting to do real AMS simulations.

The availability date of the co-simulation wasn’t clear, so today the press… Read More

AMS Design using Co-Simulation

The big three vendors in EDA offer AMS simulation tools but what about simulation choices from other EDA vendors?

It turns out there are two privately held EDA companies that have done business since the 1980’s and have just integrated a Verilog A simulator with a SPICE circuit simulator. The two companies are Aldec with a … Read More

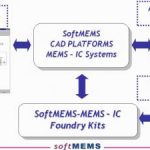

MEMS and IC Co-design

This morning I attended a webinar about MEMS and IC co-design from a company called SoftMEMS along with Tanner EDA. I learned that you can co-design MEMS and IC either in a bottom-up or top-down methodology, and that this particular flow has import/export options to fit in with your mechanical simulation tools (Ansys, Comsol, Open… Read More

How Co-design of MEMS-IC Saves Time

I learned about MEMS layout automation at a webinar in December and plan to attend another webinar next week on April 10thwhere two companies have created a MEMS-IC co-design flow, Tanner EDA and SoftMEMS. The big challenge is to ensure that the MEMS and electronic parts of a new design will simulate correctly before committing … Read More