In the rapidly evolving world of high-performance computing (HPC) and artificial intelligence (AI), technological advancements must keep pace with increasing demands for speed, efficiency, and security. Synopsys recently announced the industry’s first complete PCIe 7.0 IP solution. This groundbreaking initiative addresses… Read More

Tag: synopsys

Synopsys-AMD Webinar: Advancing 3DIC Design Through Next-Generation Solutions

Introduction of 2.5D and 3D multi-die based products are helping extend the boundaries of Moore’s Law, overcoming limitations in speed and capacity for high-end computational tasks. In spite of its critical function within the 3DIC paradigm, the interposer die’s role and related challenges are often neither fully comprehended… Read More

CEO Interview: Dr. Nasib Naser of ORION VLSI Technologies.

Dr. Nasib Naser brings over 35 years of experience in the field. His expertise spans the entire VLSI cycle from conception to chip design, with a strong focus on verification methodologies. For his 17 years at Synopsys, Dr. Naser have held senior management positions, leading North American Verification IP, managing Central … Read More

Podcast EP221: The Importance of Design Robustness with Mayukh Bhattacharya

Dan is joined by Mayukh Bhattacharya, Engineering, Executive Director, at Synopsys. Mayukh has been with Synopsys since 2003. For the first 14 years, he made many technical contributions to PrimeSim XA. Currently, he leads R&D teams for PrimeSim Design Robustness and PrimeSim Custom Fault products. He was one of the early… Read More

Podcast EP219: How Synopsys Addresses Debug and Coverage Closure Challenges with Robert Ruiz

Dan is joined by Robert Ruiz, product management director responsible for strategy and business growth of several verification products at Synopsys. Robert has held various marketing and technical positions for leading functional verification and test automation products at various companies including Synopsys, Novas… Read More

Semi Market Decreased by 8% in 2023… When Design IP Sales Grew by 6%!

Design IP revenues had achieved $7.04B in 2023, with disparity between license, growing by 14% and royalty decreasing by 6%, and main categories. Processor (CPU, DSP, GPU & ISP) slightly growing by 3.4% when Physical (SRAM Memory Compiler, Flash Memory Compiler, Library and I/O, AMS, Wireless Interface) slightly decreasing… Read More

Early SoC Dynamic Power Analysis Needs Hardware Emulation

The relentless pursuit for maximizing performance in semiconductor development is now matched by the crucial need to minimize energy consumption.

Traditional simulation-based power analysis methods face insurmountable challenges to accurately capture complex designs activities in real-world scenarios. As the scale… Read More

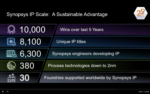

Synopsys Design IP for Modern SoCs and Multi-Die Systems

Semiconductor intellectual property (IP) plays a critical role in modern system-on-chip (SoC) designs. That’s not surprising given that modern SoCs are highly complex designs that leverage already proven building blocks such as processors, interfaces, foundational IP, on-chip bus fabrics, security IP, and others. This… Read More

Scaling Data Center Infrastructure for the Terabit Era

Earlier this month, SemiWiki wrote about Synopsys’s complete 1.6T Ethernet IP solution to drive AI and Hyperscale Data Center chips. A technology’s success is all about when, where and how it gets adopted within the ecosystem. In the high-speed ethernet ecosystem, the swift adoption of 1.6T Ethernet relies on key roles and coordinated… Read More

TSMC and Synopsys Bring Breakthrough NVIDIA Computational Lithography Platform to Production

NVIDIA cuLitho Accelerates Semiconductor Manufacturing’s Most Compute-Intensive Workload by 40-60x, Opens Industry to New Generative AI Algorithms.

An incredible example of semiconductor industry partnerships was revealed during the Synopsys User Group (SNUG) last month. It started with a press release but there is much… Read More