Now that the dust has settled, I will give you my take on the Intel Foundry event. Some might call me a semiconductor event critic as I have attended hundreds of them over the last 40 years starting with the Design Automation Conference in 1984. Foundry events are my favorite because they really are the pulse of the semiconductor industry,… Read More

Tag: synopsys

Webinar: Intel Presents: Modern EDA Solutions for Scalable Heterogeneous Systems

Featured Speakers:

- Vivek Rajan, Sr. Principal Engineer, Intel

- Amlendu Choubey, Sr. Director, Product Management, Synopsys

Why You Should Attend:

Rapidly emerging new workloads and disruptive architectures have highlighted the importance of advanced packaging and 3DIC technologies. The scaling of Moore’s Law has pushed… Read More

Webinar: Application-Specific Processors (ASIPs) for Wireless Communication SoCs

Featured Speakers:

- Dr. Falco Munsche, Technical Product Marketing, Synopsys

- Junsu Heo, SoC Design Lab, Konkuk University, Korea

Learn about:

- Synopsys ASIP Designer, the industry-leading tool to explore, design and optimize application-specific processors

- ASIP design methodology to address challenges in modern wireless

Scaling AI Infrastructure with Next-Gen Interconnects

At the recent IPSoC Conference in Silicon Valley, Aparna Tarde gave a talk on the importance of Next-Gen Interconnects to scale AI infrastructure. Aparna is a Sr. Technical Product Manager at Synopsys. A synthesis of the salient points from her talk follows.

The rapid advancement of artificial intelligence (AI) is fundamentally… Read More

Webinar: AMD Presents: 3D Odyssey – Navigating the Depths of 3DIC Feasibility Analysis

Date: May 21, 2025 | 10:00 AM PDT

Featured Speakers:

- Nitin Navale, Principal Member of Technical Staff, AMD

- Amlendu Choubey, Sr. Director, Product Management, Synopsys

Why You Should Attend:

With the rising demand for highly efficient 3DIC design and performance, it’s crucial to understand the IR and thermal landscape of a

Webinar: In-Field RAS Challenges with Chiplets and AI-based Systems

Featured Speakers:

- Jyotika Athavale, Director, Engineering Architecture, Synopsys

- Yervant Zorian, Chief Architect & Fellow, Synopsys

Abstract:

Advancements in data center and automotive System-on-Chips (SoCs) to meet AI workload demands have resulted in the increased adoption of emerging technology nodes and chiplet… Read More

Webinar: Boost Verification Efficiency with VC Execution Manager: Harnessing AI/ML for Superior Regression Management

Featured Speakers:

- Gopinath Lakshmi Narasimhan, Sr. Architect Applications Engineer

- Robert Ruiz, Sr. Director, Product Management

Why You Should Attend:

- Discover the innovative capabilities of Synopsys VC Execution Manager for streamlined verification processes.

- Learn about the seamless integration of advanced AI/ML

Achieving Seamless 1.6 Tbps Interoperability for High BW HPC AI/ML SoCs: A Technical Webinar with Samtec and Synopsys

HPC Bandwidth Explosion and 1.6T Ecosystem Interop Need

The exponential growth in data bandwidth requirements driven by HPC systems, AI, and ML applications has set the stage for an ever-increasing need for 1.6Tbps Ethernet. As data centers strive to manage vast data transfers with maximum efficiency, the urgency for interoperability… Read More

SNUG 2025: A Watershed Moment for EDA – Part 1

Hot on the heels of DVConUS 2025, the 35th annual Synopsys User Group (SNUG) Conference made its mark as a defining moment in the evolution of Synopsys—and the broader electronic design automation (EDA) industry. This year’s milestone event not only underscored Synopsys’ continued innovation but also affirmed the vision… Read More

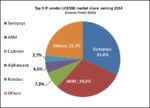

Design IP Market Increased by All-time-high: 20% in 2024!

Design IP revenues achieved $8.5B in 2024 and this is an all-time-high growth of 20%. Wired Interface is still driving Design IP growth with 23.5% but we see the Processor category also growing by 22.4% in 2024. This is consistent with the Top 4 IP companies made of ARM (mostly focused on processor) and a team leading wired interface… Read More