When I first saw that Rob Knoth (Product Director at Cadence) had proposed this topic as a subject for a blog, my reaction was “well, how accurate can that be?” I’ve been around the power business for a while, so I should know better. It’s interesting that I jumped straight to that one metric for QoR; I suspect many others will do the same.… Read More

Tag: stratus

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

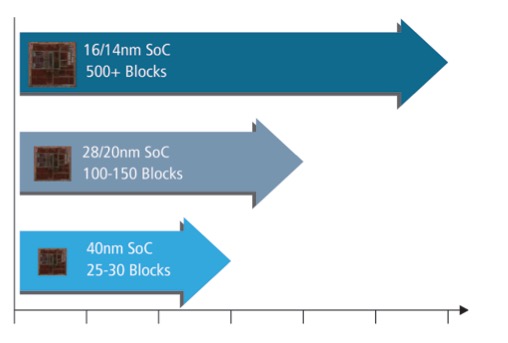

Logic Synthesis Reborn

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

High Level Synthesis Gets Stronger

High Level Synthesis (HLS) tools have been around for at least two decades now, and you may recall that about one year ago Cadence acquired Forte. The whole promise of HLS is to provide more design and verification productivity by raising the design abstraction from RTL code up to SystemC, C or C++ code. With any acquisition it is natural… Read More