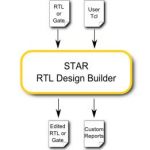

DeFacto and their STAR technology are already quite well known among those who want to procedurally apply edits to system-level RTL. I’m not talking here about the kind of edits you would make with your standard edit tools. Rather these are the more convoluted sort of changes you might attempt with Perl (or perhaps Python these days).… Read More

Tag: star

Design Deconstruction

It is self-evident that large systems of any type would not be possible without hierarchical design. Decomposing a large system objective into subsystems, and subsystems of subsystems, has multiple benefits. Smaller subsystems can be more easily understood and better tested when built, robust 3[SUP]rd[/SUP] party alternatives… Read More

Webinar: How RTL Design Restructuring Helps Meet PPA

To paraphrase an Austen line, it is a truth universally acknowledged that implementation, power intent and design hierarchy don’t always align very well. Hierarchy is an artifact of legacy structure, reuse and division of labor, perhaps well-structured piecewise for other designs but not necessarily so for the design you now… Read More

A Versatile Design Platform with Multi-Language APIs

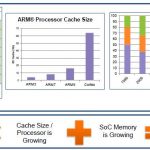

In one of my whitepapers “SoCs in New Context – Look beyond PPA”, I had mentioned about several considerations which have become very important in addition to power, performance, and area (PPA) of an SoC. This whitepaper was also posted in parts as blogs on Semiwiki (links are mentioned below). Two important… Read More

eSilicon Truly Puts the ‘e’ in Silicon

eSilicon have a new website. Companies update their websites regularly, so why is this news? Well, eSilicon increasingly does their business on the web. They are not like Facebook, say, where their business is entirely web-based, there is a physical business behind them. So they are more like Lyft for chips. Obviously Lyft requires… Read More

eSilicon Lyfts Its Game

We have got used to services like Uber and Lyft (at least in cities that are not so anti-consumer as to ban them, I’m looking at you New York. Et vous Paris). But in most of the semiconductor world we are still stuck standing at the side of the road waving our hand helplessly in the hope that the light on that taxi is actually on. Leading… Read More

How much SRAM proportion could be integrated in SoC at 20 nm and below?

Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More

Synopsys STAR Webinar, embedded memory test and repair solutions

The acquisitions of Virage Logic by Synopsys in 2010, have allowed building a stronger, diversified IP port-folio, including the embedded SRAM, embedded non-volatile memory and embedded test and repair solution. Looking back in time, I remember the end of the 80’s: at that time the up-to-date solution to embed SRAM in your ASIC… Read More