Founded in 1984, Silvaco is now the largest privately held EDA company with a rich history including a recent transformation that is worth a blog if not a book. Coincidently, I started my career in Silicon Valley in 1984 and have had many dealings with Silvaco over the years including a personal relationship with Silvaco founder … Read More

Tag: silvaco

DAC 2017: How Oracle does Reliability Simulation when designing SPARC

Last week at #54DAC there was a talk by Michael Yu from the CAD group of Oracle who discussed how they designed their latest generation of SPARC chips, with an emphasis on the reliability simulations. The three features of the latest SPARC family of chips are:

- Security in silicon

- SQL in silicon

- World’s fastest microprocessor

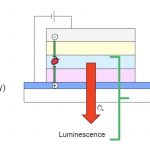

An Approach to TFT and FPD Design

Webinars are a powerful way for engineers to get updated on EDA and IC design approaches, so I’m sharing what I viewed last month at a Silvaco webinar on TFT and FPD design. You probably are using a TFT LCD display in your TV, monitor, mobile phone, video game system, GPS device or projector. The custom IC design flow offered by… Read More

TCAD for TFT, LCD and OLED Displays

As I write there are multiple displays in front of me that use TFT, LCD or OLED displays:

- ViewSonic Monitors with 24″ display

- MacBook Pro with 15″ display

- iPad Air

- Samsung Galaxy Note 4

- Nexus 7 tablet

- Garmin Edge 820

FD-SOI in Japan?

If you want to get your finger on the Japan FD-SOI pulse, registration is still open for a free, two-day workshop in Tokyo this week organized by the SOI Consortium. This is the 3rd Annual SOI Tokyo Workshop, and there’s a really interesting line-up of speakers.

In case you’re wondering, Japan is doing FD-SOI. In fact… Read More

Webinar on TFT and FPD Design

I knew that the acronym for TFT meant Thin Film Transistors, but I hadn’t heard that FPD stands for Flat Panel Detectors. It turns out the FPD are solid-state sensors used in x-ray applications, similar in operation to image sensors for digital photography and video. I’ll be attending and blogging about what I learn… Read More

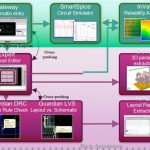

Approaches for EM, IR and Thermal Analysis of ICs

As an engineer I’ve learned how to trade off using various EDA tools based on the accuracy requirements and the time available to complete a project. EDA vendors have been offering software tools to help us with reliability concerns like EM, IR drop and thermal analysis for several years now. Last week I attended a webinar … Read More

The Importance of EM, IR and Thermal Analysis for IC Design – Webinar

Designing an IC has both a logical and physical aspect to it, so while the logic in your next chip may be bug-free and meet the spec, how do you know if the physical layout will be reliable in terms of EM (electro-migration), IR (voltage drops) and thermal issues? EDA software once again comes to our rescue to perform the specific type… Read More

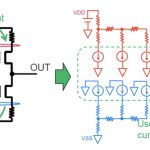

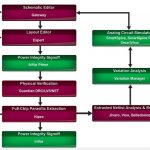

Analyzing All of those IC Parasitic Extraction Results

Back at DAC in 2011 I first started to hear about this EDA company named edXact that specialized in reducing and analyzing IC parasitic extraction results. So Silvaco acquired edXact and I wanted to get an update on what is new with their EDA tools that help help you to analyze and manage the massive amount of extracted RLC and even K … Read More

What You Don’t Know about Parasitic Extraction for IC Design

Out of college my first job was doing circuit design at the transistor-level with Intel, and to get accurate SPICE netlists for simulation we had to manually count the squares of parasitic interconnect for diffusion, poly-silicon and metal layers. Talk about a burden and chance for mistakes, I’m so thankful that EDA companies… Read More