Exciting times for the semiconductor industry! Last week Intel announced a billion dollar fund to build a foundry ecosystem and today Intel announced they are acquiring foundry Tower Semiconductor for $5.6 billion dollars, WOW! Some people doubted Intel’s commitment to the foundry market this time. I think we can now put that… Read More

Tag: silicon creations

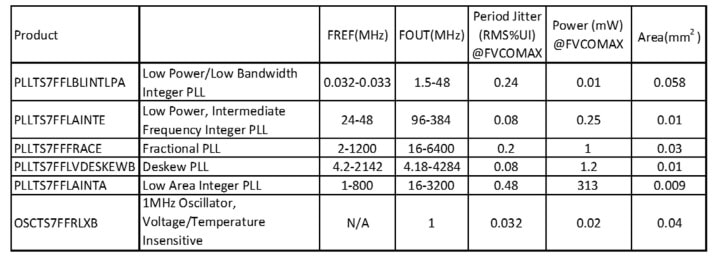

Creating Analog PLL IP for TSMC 5nm and 3nm

TSMC’s Open Innovation Platform’s main objective is to create and promote partnership for producing chips. This year’s OIP event included a presentation on the joint efforts of Silicon Creations, Mentor, a Siemens business and TSMC to produce essential PLL IP for 5nm and 3nm designs. The relentless push for smaller geometries… Read More

Design IP in 2018: Synopsys and Cadence Increase Market Share…

…but ARM, Imagination, MIPS or Ceva have declined and lose market share. Semiconductor design IP market is still doing good in 2018, with 6% growth year over year. It’s half the growth rate seen in 2017, 2016 and 2015 and the growth decline is imputable to bad results from ARM, the market leader, but also from Imagination (#4), MIPS… Read More

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

Keeping Pace With 5nm Heartbeat

A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power… Read More

DAC 2018 Potpourri

The venue

Despite of being held at the new three-story Moscone West building, this year 55th DAC in San Francisco bore many similarities as compared with last year’s. Similar booth decors and floorplan positioning of the big two, Synopsys and Cadence, which were across of each other and right next to the first floor entrance –although… Read More

TSMC OIP DAC Theater Schedule 2018

The TSMC OIP DAC Theater schedule is finalized and ready to go. It kicks off Monday at 10:15 am in booth #1629 and ends with a raffle at 5:45 pm each day (Mon-Tue-Wed) TSMC gives out some very nice prizes so check in with the TSMC booth staff when you arrive. There are 66 coveted presentation spots representing the top ecosystem partners… Read More

Context is Everything – especially for autonomous vehicle IP

GM has just announced that it will introduce a car with no steering wheel or pedals in 2019. According to their statement, they have already planned four phases of their autonomous driving system, and they will plan many more. However, before we jump into this latest car and not grab the wheel for a spin, it is reasonable to ask about… Read More

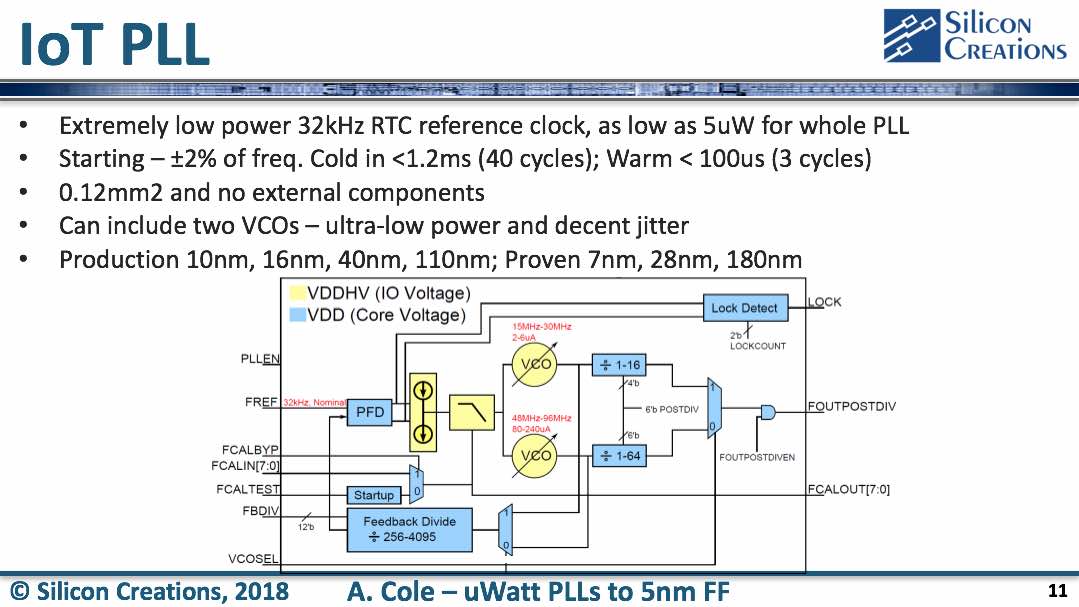

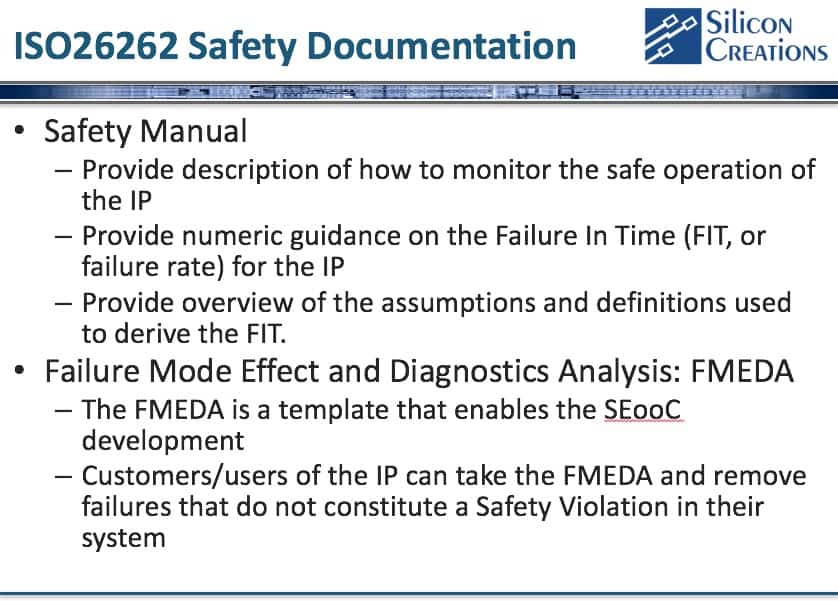

Safety qualification for leading edge IP elements – presentation at REUSE 2017 in Santa Clara

To ensure the reliability of automotive electronics, standards like AEC-Q100 and ISO 26262 have helped tremendously. They have created rational and explicit steps for developing and testing the electronic systems that go into our cars. These are not some abstract future requirement for fully autonomous cars, rather they are… Read More

Silicon Creations talks about 7nm IP Verification for AMS Circuits

Designing at 7nm is a big deal because of the costs to make masks and then produce silicon that yields at an acceptable level, and Silicon Creations is one company that has the experience in designing AMS IP like: PLL, Serializer-Deserializer, IOs, Oscillators. Why design at 7nm? Lots of reasons – lower power, higher speeds,… Read More