The difficulty of SoC integration is clearly getting more demanding. Driven by process node density, multi-chip integration and seemingly never-ending demands for more performance at lower power, the hurdles continue to increase. When you consider these challenges in the context of Arteris, it’s natural to think about hardware… Read More

Tag: rtl restructuring

Physically Aware SoC Assembly

We used to be comfortable with the idea that the worlds of logical design and physical implementation could be largely separated. Toss the logical design over the wall, and the synthesis and P&R teams would take care of the rest. That idea took a bit of a hit when we realized that synthesis had to become physically aware. The synthesis… Read More

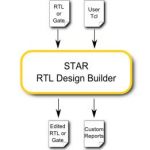

Another Application of Automated RTL Editing

DeFacto and their STAR technology are already quite well known among those who want to procedurally apply edits to system-level RTL. I’m not talking here about the kind of edits you would make with your standard edit tools. Rather these are the more convoluted sort of changes you might attempt with Perl (or perhaps Python these days).… Read More

Webinar: How RTL Design Restructuring Helps Meet PPA

To paraphrase an Austen line, it is a truth universally acknowledged that implementation, power intent and design hierarchy don’t always align very well. Hierarchy is an artifact of legacy structure, reuse and division of labor, perhaps well-structured piecewise for other designs but not necessarily so for the design you now… Read More

CEO Interview: Chouki Aktouf of Defacto Technologies

As a 30+ year semiconductor veteran I can tell you with 100% certainty that start-ups are the lifeblood of EDA. The mantra is “Innovate or Die!” and that is exactly what Defacto is doing. After more than 10 years of innovating in Design for Test at RTL, Defacto is now offering a complete EDA solution based on generic EDA… Read More

Automatic RTL Restructuring: A Need Rather Than Convenience

In the semiconductor design industry, most of the designs are created and optimized at the RTL level, mainly through home grown scripts or manual methods. As there can be several iterations in optimizing the hierarchy for physical implementation, it’s too late to do the hierarchical optimizations after reaching the floor plan… Read More