You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

IMS2026by Admin on 12-11-2025 at 1:32 pm

The IEEE International MTT Symposia (IMS) (www.ims-ieee.org) is the world’s premier RF/microwave technical conference and industry exhibition. Attendees will appreciate that IMS2026 has been refreshed with the technical content reorganized, and new branding, new website, and new mobile app launched.

…

Read More

By Jason Liu, RFIC-GPT Inc.

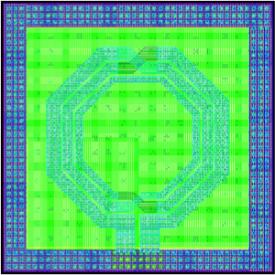

Radio frequency integrated circuits (RFICs) have become increasingly critical in modern electronic systems, driven by the rapid growth of wireless communication technologies (5G/6G), the Internet of Things (IoT), and advanced radar systems. With the desire for lower power consumption, higher… Read More

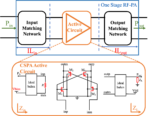

In the rapidly evolving world of Radio Frequency Integrated Circuits (RFIC), the challenge has always been to design efficient, high-performance components quickly and accurately. Traditional methods, while effective, come with a high complexity and a lengthy iteration process. Today, we’re excited to unveil RFIC-GPT… Read More

Compute environments have advanced significantly over the past several years. Microprocessors have gotten faster by including more cores, available RAM has increased significantly, and the cloud has made massive distributed computing more easily and cheaply available.

HFSS has evolved to take advantage of these new capabilities,… Read More

It seems that it has always been that there were packages and ICs, and in the design tool world “never the twain shall meet”. The tools for designing packages were completely separate from the tools used to design IC’s. This was so profoundly true that even after Cadence merged with Valid Logic back in the early 90’s, their Allegro … Read More

RFIC developers used to favor mature silicon processes, typically staying back a couple of nodes behind the leading edge. This bought foundries time for ‘RF-enabling’ their PDKs, and also maximized return on investment for developing RF models and infrastructure IP. Not the case any more, it seems. To address the insatiable … Read More