PCI Express (PCIe) has become an important communication element in a wide range of systems. It is used to connect networking, storage, FPGA and GPGPU boards to servers and desktop systems. It has progressed a long way from its initial parallel bus format. Its evolution to a serial point to point configuration has been accompanied… Read More

Tag: questa

Mentor at DVCON 2020!

Are you ready for the premier conference for functional design and verification of electronic systems?

Sponsored by Accellera Systems Initiative, DVCon is an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP)… Read More

Mentor’s Questa verification tools now run on 64-bit ARM based servers

The server market has been undergoing changes in the last few years. The traditional go-to for server processors had been x86 based chips from Intel or AMD. However, if you go on Amazon AWS looking for EC2 instances, you will see the “A1” instance type, which is an ARM based instance. This is not what you might think at first. The A1 instance… Read More

MENTOR at DVCON 2019

The semiconductor conference season has started out strong and the premier verification gathering is coming up at the end of this month. SemiWiki bloggers, myself included, will be at the conference covering verification so you don’t have to. Verification is consuming more and more of the design cycle so I expect this event to … Read More

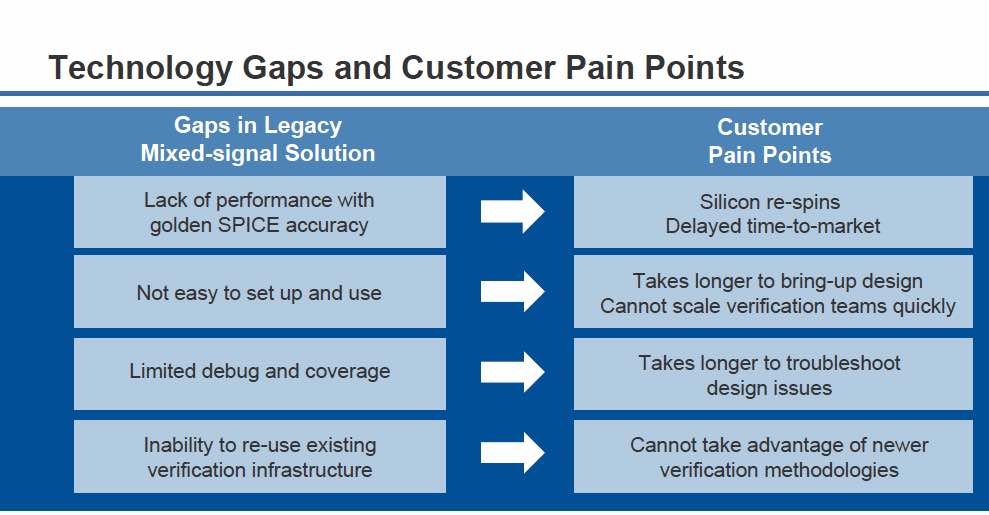

Mentor’s Symphony in Tune with AMS Designer Needs

Mixed signal simulation is a very hot topic these days. In modern designs, it is harder to draw a line between the analog and digital and work with them independently. Analog blocks are showing up everywhere. Even in what would have qualified as a digital design a few years ago, now designers need to look at things like PLLs, IOs and … Read More

Portable Stimulus enables new design and verification methodologies

My usual practice when investing is to look at startup companies and try to understand if the market they are looking to serve has a significant opportunity for a new and disruptive technology. This piece compiles the ideas that I used to form an investment thesis in Portable Stimulus. Once collected, I often share ideas to get feedback.… Read More

Shifting Low Power Verification to an IP to SoC Flow

One of the most exciting recent developments in low power design and verification is the successive refinement flow developed by ARM® and Mentor Graphics®.… Read More

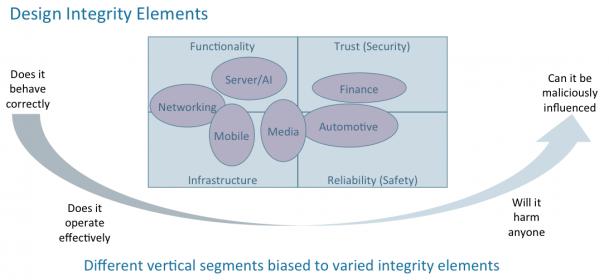

Something Old, Something New…EDA and Verification

When I got the opportunity to blog about verification, I thought, what new and interesting things should I talk about? Having started my EDA career in 1983, I often feel like one of the “oldies” in this business…remember when a hard drive required a static strap, held a whopping 33 MB, and was the size of a brick? Perhaps they should … Read More

Never Imagined So Easy Class-based Testbench Debugging

When it comes to debugging a design testbench organized in object-oriented style with objects, component hierarchies, macros, transactions and so on, it becomes an onerous, tasteless, and thankless task for RTL verification engineers who generally lag in software expertise. Moreover, class-based debugging tools have lagged… Read More

Power Management Gets Tricky in IP Driven World

Today, an SoC can have multiple instances of an IP and also instances of many different IPs from different vendors. Every instance of an IP can work in a separate mode and requires a dedicated power arrangement which may only be formalized at the implementation stage. The power intent, if specified earlier, will need to be re-generated… Read More