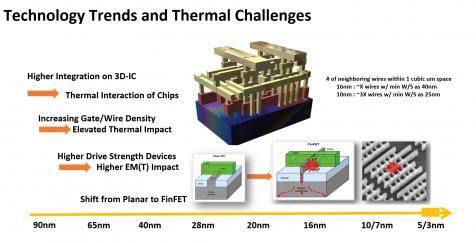

Thermal considerations have always been a concern in electronic systems but to a large extent these could be relatively well partitioned from other concerns. Within a die you analyze for mean and peak temperatures and mitigate with package heat-sinks, options to de-rate the clock, or a variety of other methods. At the system level… Read More

Tag: power artist

Getting the Best Dynamic Power Analysis Numbers

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

Apache Power Artist Capabilities I

I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be… Read More