For the next installment in our series of semiconductor CEO interviews we meet with Randy Caplan from Silicon Creations. Randy has helped build the company from a small startup to one of the world’s leading providers of interface and clocking IP. Almost every new chip developed these days has a requirement for PLLs and SerDes. Since… Read More

Tag: pll

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

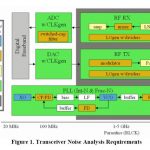

Full Spectrum Analog FastSPICE Useful for RF Designs on Bulk CMOS

It has been about a year since the acquisition of Berkeley Design Automation by Mentor Graphics. Berkeley was doing quite well in the somewhat crowded SPICE simulator market. In many respects they broke new ground for high speed and accurate SPICE simulators. Since the acquisition we know that former Berkeley executives are now… Read More

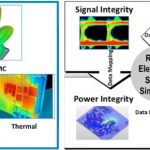

LSI’s Way of Faster & Reliable Electronic System Design

LSI Corporationstarted in 1980s and I had several encounters with it during my jobs in 1990s; not to forget the LSI chips I used to see in desktops and other electronic systems, and I’m happy to see LSI continuing today with more vigour having leadership position in storage and networking space. It provides highly reliable, high … Read More

On-Chip Clock Generation beyond Phase Locked Loop

Inside a today’s typical VLSI system, there are millions of electrical signals. They make the system perform what it is designed to do. Among those, the most important one is the clock signal. From an operational perspective, clock is the timekeeper of the electrical world inside the chip/system. From a structural perspective,… Read More

PLL Design Challenges for Integrated Circuit Designs

Nandu Bhagwan is CEO of GHz Circuits and has been designing PLL circuits used in ICs for the past 12 years. Mr. Bhagwan did a video interview with John Pierce of Cadence to talk about the challenges of PLL design.… Read More

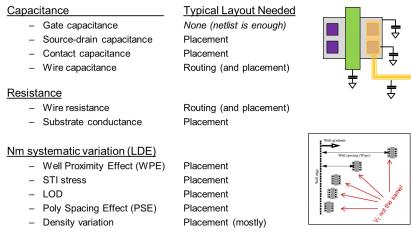

Nanometer Circuit Verification: The Catch-22 of Layout!

As analog and mixed-signal designers move to very advanced geometries, they must grapple with more and more complex considerations of the silicon. Not only do nanometer CMOS devices have limitations in terms of analog-relevant characteristics such gain and noise performance, but they also introduce new sources of variation… Read More