SoC designs use many levels of design abstraction during their journey from ideation to implementation, and now it’s possible to perform power analysis quite early in the design process. I had a call with William Ruby, Director of Porduct Marketing – Synopsys Low Power Solution to hear what they’ve engineered… Read More

Tag: platform architect

Computational Imaging Craves System-Level Design and Simulation Tools to Leverage AI in Embedded Vision

Aberration-free optics are bulky and expensive. Thanks to high-performance AI-enabled processors and GPUs with abundant processing capabilities, image quality nowadays relies more on high computing power tied to miniaturized optics and sensors. Computational imaging is the new trend in imaging and relies on the fusion … Read More

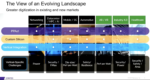

Delivering Systemic Innovation to Power the Era of SysMoore

With the slowing down of Moore’s law , the industry as a whole has been working on various ways to maintain the rate of growth and advancements. A lot has been written up about various solutions being pursued to address specific aspects. The current era is being referred to by different names, SysMoore being one that Synopsys uses.… Read More

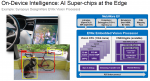

AI Hardware Summit, Report #3: Enabling On-Device Intelligence

This is the third and final blog I have written about the recent AI Hardware Summit held at the Computer History Museum in Mountain View, CA. Day 1 of the conference was more about solutions in the data center, whereas Day 2 was primarily around solutions at the Edge. This presentation from Day 2 was given by Dr. Thomas Anderson, Head,… Read More

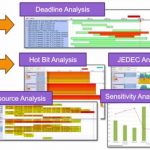

DDR stands for Don’t Do (Just) RTL

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More