You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

By Mark Tawfik

Parasitic extraction is essential in integrated circuit (IC) design, as it identifies unintended resistances, capacitances, and inductances that can impact circuit performance. These parasitic elements arise from the layout and interconnects of the circuit and can affect signal integrity, power consumption,… Read More

By Shehab Ashraf

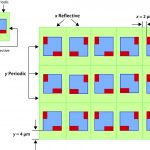

As semiconductor technology scales and device complexity increases, accurately modeling the parasitic effects of metal fill has become critical for circuit performance, power integrity, and reliability. Metal fill is a crucial part of the manufacturing process, ensuring uniform layer density, improving… Read More

As electric vehicles (EVs) gain widespread adoption, safety, reliability, and efficiency are becoming increasingly important. A crucial component in ensuring these aspects is the power module (PM), which manages the energy flow between the EV battery and the motor. The design of these power modules must not only meet the high-performance… Read More

One of the most promising advancements in the semiconductor field is the development of 3D Integrated Circuits (3D ICs). 3D ICs enable companies to partition semiconductor designs and seamlessly integrate silicon Intellectual Property (IP) at the most suitable process nodes and processes. This strategic partitioning yields… Read More

Maxim is a scientist, engineer, and entrepreneur. His expertise is in physics, mathematics, semiconductor devices, and EDA. Prior to co-founding Diakopto, Maxim worked at Apple’s SEG (Silicon Engineering Group), where he was responsible for parasitic extraction. Before Apple, he was CTO of Silicon Frontline Technology,… Read More

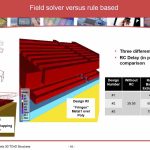

Traditional, rule based, RC extractors rely on a substantial base of assumptions, which are increasingly proving unreliable. Having accurate RC extraction results for parasitic R’s and C’s is extremely important for ensuring proper circuit operation and for optimizing performance and power. Advanced process nodes are making… Read More

EDA companies produce a wealth of content to help IC engineers get the best out of their tools through several means:

- Reference Manuals

- User Guides

- Tutorials

- Workshops

- Seminars

- Training Classes

- Phone Support

- AE visits

…

Read More

Advanced process technologies for manufacturing computer chips enable more functionality, higher performance, and low power through smaller sizes. Memory bits on a chip are predicted to double every two years to keep up with the demand for increased performance.

To meet these new requirements for performance and power, memory… Read More

Flash analog-to-digital converters (ADCs) are commonly used in high-frequency applications such as satellite communications, sampling oscilloscopes, and radar detection. Flash ADC is preferred over other ADC architectures because it is extremely fast and quite simple. However, flash ADC typically requires twice as many… Read More

By Carey Robertson, Director of Product Marketing, Mentor Graphics

IC physical verification requires a number of different types of checking, the most familiar being design rule checking (DRC), layout vs. schematic (LVS) checking, and parasitic extraction combined with circuit simulation. Fundamentally, it does not matter… Read More