Compared to the automation of digital design, the development of automation for analog has taken a much more arduous path. Over the decades there have been many projects both academic and commercial to accelerate and improve the process for analog design. One of the most interesting efforts in this area is being spearheaded by … Read More

Tag: parallel

Making Functional Simulation Faster with a Parallel Approach

I’ll never forgot working at Intel on a team designing a graphics chip when we wanted to simulate to ensure proper functionality before tapeout, however because of the long run times it was decided to make a compromise to speed things up by reducing the size of the display window to just 32×32 pixels. Well, when first silicon… Read More

Logic Synthesis Reborn

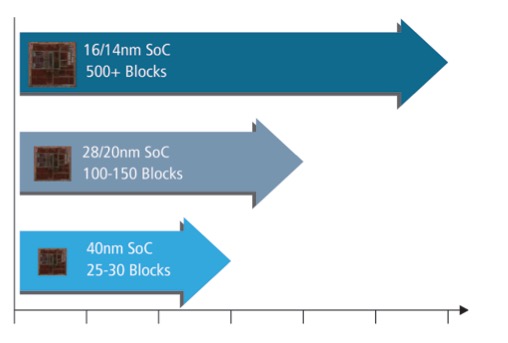

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

Gigahertz FFT rates on a 500MHz budget

A basic building block of any communication system today is the fast Fourier transform, or FFT. A big advantage of FPGA implementations of FFTs is they can be scaled and tuned for the task at hand, optimizing data flow, resource use, and power consumption. Scaled, that is, up to the clock speed of the FPGA – or so it would seem.

Today’s… Read More

EDPS: Parallel EDA

EDPS was last Thursday and Friday in Monterey. I think that this is a conference that more people would benefit from attending. Unlike some other conferences, it is almost entirely focused around user problems rather than doing a deep dive into things of limited interest. Most of the presentations are more like survey papers and… Read More