We are all pretty familiar with augmented reality, where real world images are overlaid with computer generated images, graphics and even audio. Of course, our first exposure to augmented reality might have been images of heads up displays in fighter jets or perhaps in the movie The Terminator. Augmented reality is moving rapidly… Read More

Tag: opencv

Synopsys Launch EV6x Vision Processor… Challenging the Competition!

When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 100X… Read More

OpenVX Bring Power-efficient Vision Acceleration to Mobile

OpenVX is the next open source sample specification to be launched by Khronos group, a consortium building a family of interoperating APIs for portable and power efficient vision processing. If you take a look at the OpenVX participant list, you can check that the major chip makers: Broadcom, Qualcomm, TI, Intel, Nvidia, Renesas,… Read More

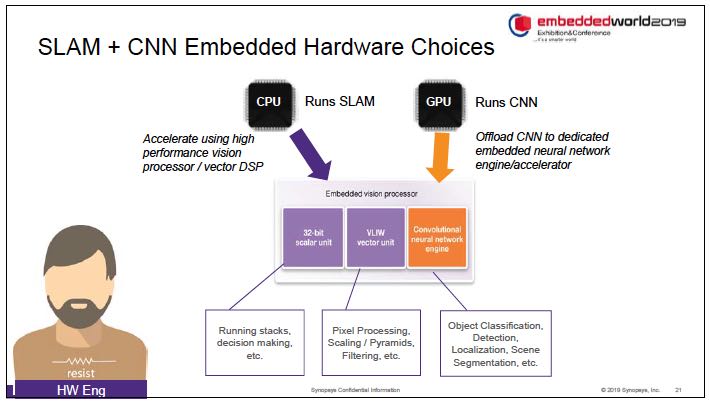

Workload-tuned cores seeing greater interest

Is it possible to design a processor with very high performance and low power consumption? To answer that, embedded illuminati are now focusing on designs tuned to specific workloads – creating a tailored processor that does a few things very efficiently, with nothing extra.… Read More

Xilinx: Hide the RTL

Tom Feist of Xilinx presented here at the GlobalPress Electronics Summit about their strategy to take design abstraction up another level. In the SoC world, we are still pretty much stuck at the RTL level and have moved to higher abstractions by using an IP strategy. But at least all IC designers are RTL-literate.

Xilinx, in the Vivado… Read More