For decades, semiconductor teams have relied on traditional methods such as corner-based analysis, surrogate monitors, and population-level statistical screening for post-silicon validation. These methods served well when variability was modest, and timing paths behaved predictably. However, today’s advanced nodes… Read More

Tag: ocv

Afraid of mesh-based clock topologies? You should be

Digital logic chips synchronize all logic operations by using a clock signal connected to flip-flops or latches, and the clock is distributed across the entire chip. The ultimate goal is to have a clock signal that arrives at the exact same moment in time at all clocked elements. If the clock arrives too early or too late from the PLL… Read More

CEO Interview: Mo Faisal of Movellus

Prior to founding Movellus, Dr. Faisal held positions at semiconductor companies such as Intel and PMC Sierra. Faisal received his B.S. from the University of Waterloo, and his M.S. and Ph.D. from the University of Michigan, and holds several patents. Dr. Faisal was named a “Top 20 Entrepreneur” by the University of Michigan Zell… Read More

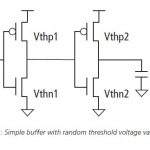

Statistically speaking you probably care about On-chip Variation

There are some metaphorical similarities between reaching timing signoff and driving a car to your destination. Most of us get in the car, turn the key and push the gas pedal to make it go. While we might have a cursory understanding of what makes it go, there are actually a lot of “moving part” under the hood in each instance. For most… Read More

Webinar: OCV and Timing Closure Sign-off by Silvaco on Oct 10 at 10AM

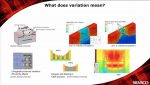

The old adage that goes the one constant thing you can always count on is change, could easily be reworded for semiconductor design to say the one constant thing you can count on is variation. This is doubly true. Not only is variation, in all its forms, a constant factor in design, additionally the methods of analyzing and dealing … Read More

We Need Libraries – Lots of Libraries

It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Solutions for Variation Analysis at 16nm and Beyond

Variation is still the tough nut to crack for advanced process nodes. The familiar refrain of lower operating voltages and higher performance requirements make process variation an extremely important design consideration. As far back as the early 2000’s design teams have been looking for a better approach to model variation… Read More

Challenges in IP Qualification with Rising Physical Data

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More

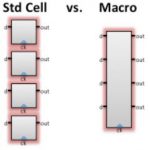

The Revenge of Microprocessor Design: The Return of the Macro

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More

Variation Alphabet Soup

On-chip variation (OCV) is a major issue in timing signoff, especially at low voltages or in 20/16/14nm processes. For example, the graph below shows a 20nm inverter. At 0.6V the inverter has a delay of 2 (nominalized) units. But due to on-chip variation this might be as low as 1.5 units or as high as 3 units, which is a difference from… Read More