As analog and mixed-signal designs become increasingly complex, parasitic effects dominate both design time and cost, consuming 30–50% of engineers’ effort in debugging and reanalyzing circuits. Addressing these multiphysics effects requires early verification strategies and reliable simulation solutions. Modern … Read More

Tag: oasis

Why IP Designers Don’t Like Surprises!

If it’s your job to get a SoC design through synthesis, timing/power closure and final verification, the last thing you need are surprises in new versions of the IP blocks that are integrated into the design. If your IP supplier sends a new version, the best possible scenario is that this is only a small incremental change from… Read More

Viewing the Largest IC Layout Files Quickly

The old adage, “Time is money”, certainly rings true today for IC designers, so the entire EDA industry has focused on this challenging goal of making tools that help speed up design and physical verification tasks like DRC (Design Rule Checks) and LVS (Layout Versus Schematic). Sure, the big three EDA vendors have… Read More

Why Open and Supported Interfaces Matter

Back in the early 1980’s during the nascent years of electronic design automation (EDA), I worked at Texas Instruments supporting what would become their merchant ASIC business. Back then, life was a bit different. The challenge we faced was to make our ASIC library available on as many EDA flows as we could to give as many users as… Read More

Cadence Sues Berkeley Design Automation

Cadence has brought a suit against Berkeley Design Automation for, as far as I can see, integrating their AFS circuit simulator with the Virtuoso Analog Design Environment (ADE) without using the (licensed) Oasis product. Since BDA is (actually was) a member of the Cadence Connections program, they have to abide by the contract… Read More

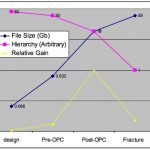

The Need for OASIS in Post-layout IC Databases

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

Dawn at the OASIS, Dusk for GDSII

For an industry committed to constant innovation, changes in any part of the design flow are only slowly adopted, and only when absolutely necessary. Almost 10 years ago, it became clear that shrinking process technologies would bring a massive growth of layout and mask data—rougly 50% per node. This avalanche of data seriously… Read More