As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

Tag: noise

Reliability sign-off has several aspects – One Solution

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Designing for Reliability

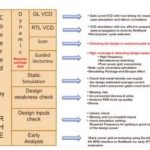

Analyzing the operation of a modern SoC, especially analyzing its power distribution network (PDN) is getting more and more complex. Today’s SoCs no longer operate on a continuous basis, instead functional blocks on the IC are only powered up to execute the operation that is required and then they go into a standby mode, … Read More

Noise Coupling

One of the challenges of designing a modern SoC is that the digital parts of the circuit are really something that in an ideal world you’d keep as far away from the analog as possible. The digital parts of the circuit generate large amounts of noise, especially in the power supply and in the substrate, two areas where it is impossible… Read More

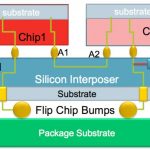

2.5D and 3D designs

Going up! Power and performance issues, along with manufacturing yield issues, limit how much bigger chips can get in two dimensions. That, and the fact that you can’t manufacture two different processes on the same wafer, mean that we are going up into the third dimension.

The simplest way is what is called package-in-package… Read More

Totem webinar: Analog/Mixed-Signal Power Noise and Reliability

The Totem webinar will be at 11am on Tuesday 2nd August. This session will be conducted by Karan Sahni, Senior Applications Engineer at Apache Design Solutions. Karan has been with Apache since 2008, supporting the Redhawk, Totem, Sentinel product lines. He received his MS in Electrical Engineering from the Syracuse University… Read More