SoCs face a lot of issues related to security and the Network-on-Chip (NoC) is in a good position to facilitate system-wide services. SoCs are now so complex that one of the challenges is to make sure that the chip does what it is meant to do and doesn’t do what it isn’t meant to do. Just as in software, security used to be … Read More

Tag: noc

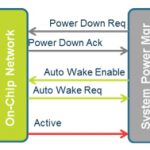

5 Rules of Power Management Using NoCs

If it has escaped your notice that power management on SoCs is important then you need to get out more. Increasingly, the complexity of the interconnect between the various processors, memories, offload processors, devices, interfaces and other blocks means that the best way to implement it is to use a network on chip (NoC). But… Read More

Qualcomm and Arteris: the CEO Speaks

Arteris finally announced this morning, as rumored, that Qualcomm is acquiring “certain technology assets” and hired personnel formerly employed by Arteris. The financial terms were not disclosed.

I talked to Charlie Janac, the CEO, today. The first thing I asked him is why such a convoluted deal, I’ve never… Read More

Qualcomm Arteris deal

Is it really a surprise if Qualcomm, the undisputed leader of Application Processor (AP) and BaseBand (BB) IC for wireless mobile, already one of the Arteris investors (with ARM, Synopsys, Docomo Capital and a bunch of VC), eventually acquires the best NoC IP technology (the technology, the engineering team and the rights, but… Read More

Open Letter from Sonics to Arteris

I don’t remember seeing an open letter from one EDA or IP company to another until today. Sonics have published an open letter to Charlie Janac, the CEO of Arteris. What seems to have happened is that Arteris have sold their assets to Qualcomm and the development team (which is based in France) and several AEs are already Qualcomm… Read More

Let’s comment… a comment from Sonics (about Arteris)

We still don’t know the precise status about a potential acquisition of Arteris by Qualcomm, and I prefer not to comment a rumor and wait for the official announcement, if any. But I would like to comment … a comment about this rumor, recently made by Sonics. This comment has taken the form of an Open Letter, from “Grant Pierce, CEO of… Read More

History of SoC Interconnect Fabric

I just read this very interesting article posted by Kurt Shuler from Arteris, describing the “History of SoC Interconnect Fabric” and explaining why the SC industry needs an advanced approach, named the “fourth phase of the Interconnect Fabric history” in the article. Kurt’s point of view is that in the past the SoC interconnect… Read More

What Does Sports and NoC Have in Common?

As an Oakland Raider season ticket holder I attend as many Raider home games as possible. If you have ever attended a live sporting event at a large stadium, and you travelled by car, you are probably familiar with the traffic problems that occur at the end of the game when everyone wants to leave the stadium parking lot at the same time.… Read More

Security Needs in On-Chip Networks

I remember during my first ten years as a software developer, I used many different computers such as IBM mainframes, Apollo and Sun workstations, and VAX computers. During that time I also bought my first home computer, a Macintosh. I didn’t of course think of this at the time, but the one thing they all had in common was that they did… Read More

NoC adoption surge at Chinese chip maker

The news from Arteris, Inc., announcing that “its interconnect fabric IP has been licensed and deployed in a majority of chips developed by China’s leading semiconductor companies for applications including consumer electronics, smartphones, and tablets,” is holding attention for several reasons. At first, because it’s… Read More