Key Takeaways:

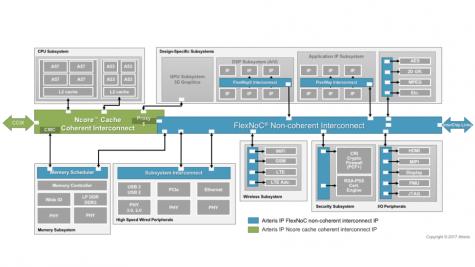

- Expanded Multi-Die Solution: Arteris showcases its foundational technology for rapid chiplet-based innovation. Check out the multi-die highlights video.

- Ecosystem compatibility: Supported through integration with products from major EDA and foundry partners, including Cadence, Synopsys, and global