TSMC is the leading foundry worldwide and they make a big splash each year at the DAC exhibit and conference, so I stopped by their theatre area during the presentation from IP vendor Moortec to see what’s new this year. Stephen Crosher was the presenter from Moortec and we had exchanged emails before, so this was the first time… Read More

Tag: moortec

Monitoring Process, Voltage and Temperature in SoCs, webinar recap

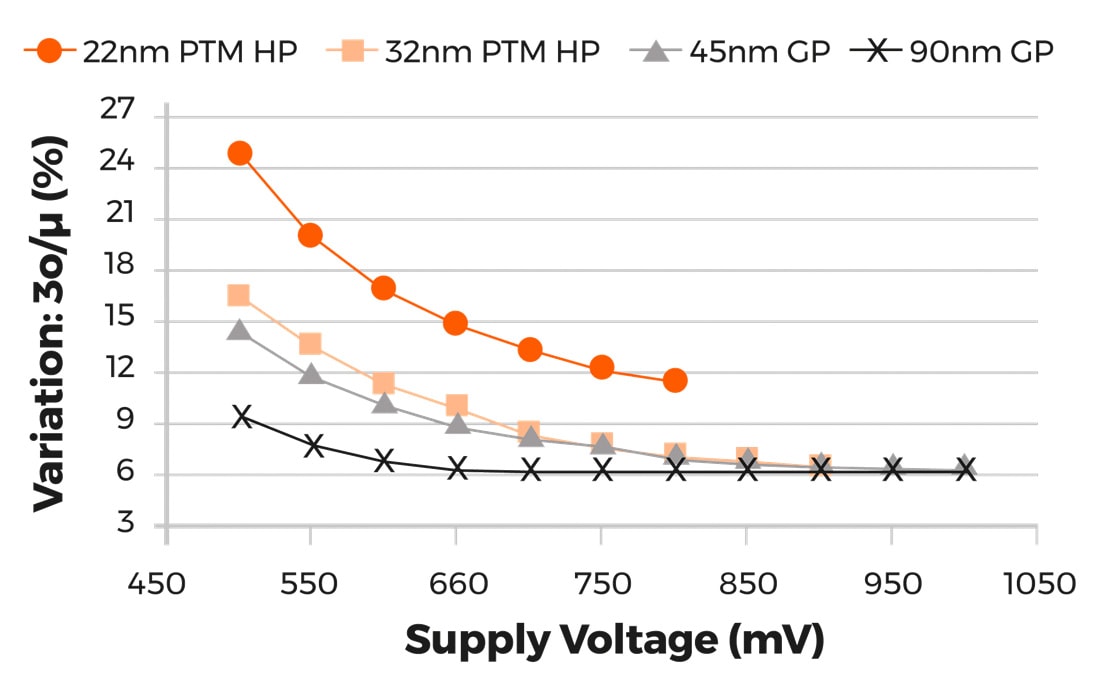

Have you ever wondered how process variation, thermal self-heating and Vdd levels affect the timing and yield of your SoC design? If you’re clock specification calls for 3GHz, while your silicon is only yielding at 2.4GHz, then you have a big problem on your hands. Such are the concerns of many modern day chip designers. To… Read More

Webinar Alert – Embedded Monitoring of Process and Voltage in SoCs

In the old days to learn about new semiconductor IP you would have to schedule a sales call, listen to the pitch, then decide if the IP was promising or not. Today we have webinars which offer a lot less drama than a sales call, plus you get to ask your questions by typing away at the comfort of your desk, hopefully wearing headphones as … Read More

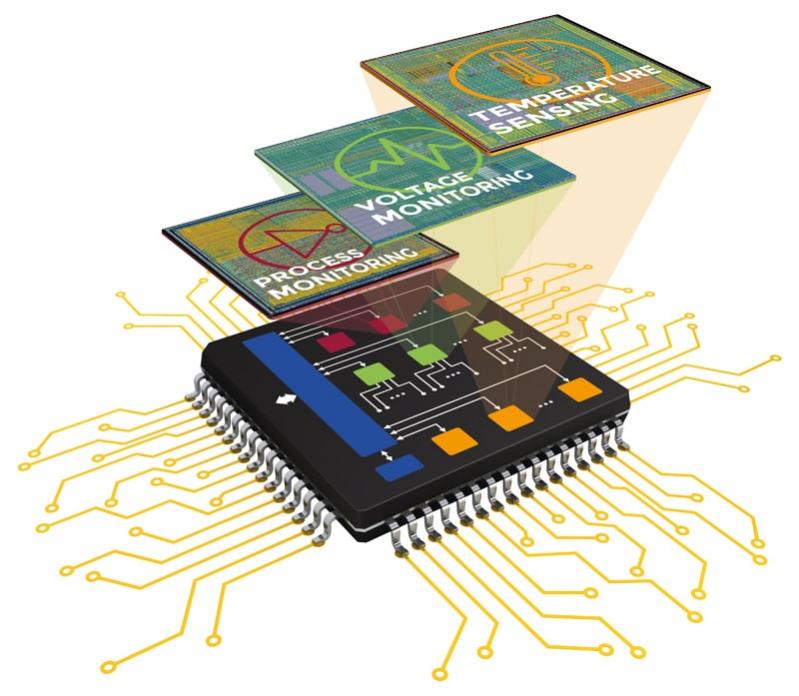

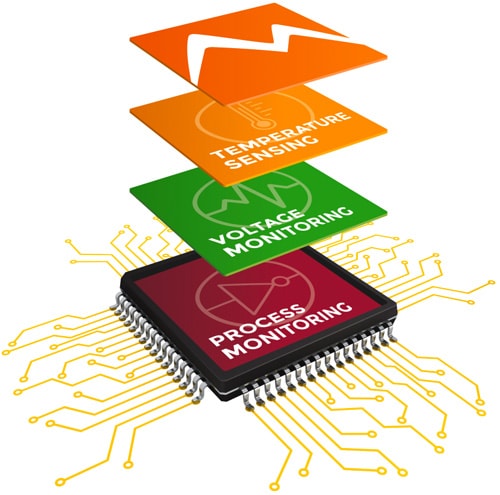

Why It’s A Good Idea to Embed PVT Monitoring IP in SoCs

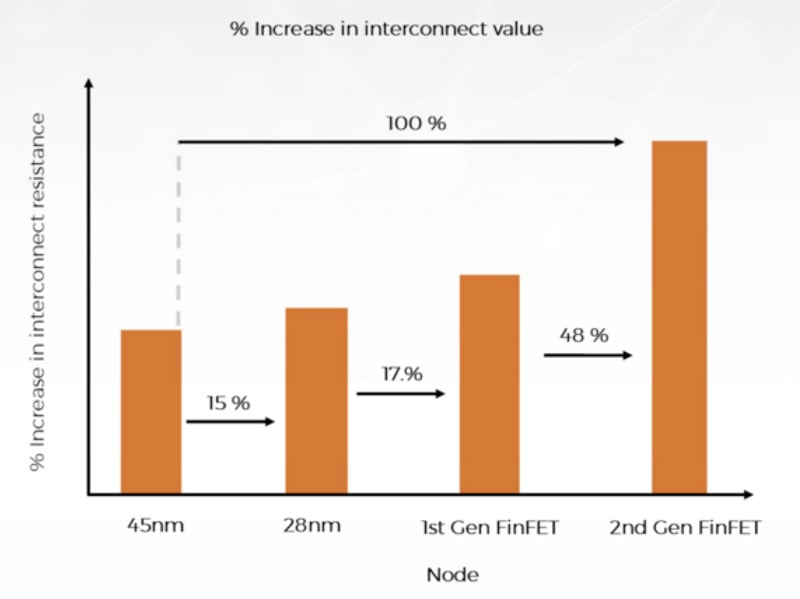

At Intel back in the late 1970’s we wanted to know what process corner each DRAM chip and wafer was trending at so we included a handful of test transistors in the scribe lines between the active die. Having test transistors meant that we could do a quick electrical test at wafer probe time to measure the P and N channel transistor… Read More

Moore’s Law Drives Foundries and IP Providers

2017 was a banner year for semiconductor sales as they topped $400B for the first time, an increase of some 20%, there is happiness in Silicon Valley, Taiwan, South Korea, and well, everywhere. With the foundries pushing to ever-smaller process dimensions and even going back to mature nodes and offering more variations that are… Read More

Embedded In-chip Monitoring, Webinar Recap

Six years ago I first interviewed Stephen Crosher, CEO and Co-founder of Moortecas they were in startup mode with some new semiconductor IP for temperature sensing, and earlier this month I attended their webinar all about embedded in-chip monitoring to get caught up with their technology and growing success. Ramsay Allen is … Read More

Making Your Next Chip Self-Aware

One holy grail of AI software developers is to create a system that is self-aware, or sentient. A less lofty goal than sentient AI is for chip designers to know how each specific chip responds to Process variations, Voltage levels and Temperature changes. If a design engineer knew exactly which process corner that each chip was fabricated… Read More

Analog IP Design at Moortec

Stephen Crosher started up Moortec in the UK back in 2005 with the help of his former Zarlink co-workers and they set to work offering AMS design services and eventually created their own Analog IP like the temperature sensor shown below:

We spoke by phone last week about his start-up experience and how they approach AMS design.… Read More