Lauro Rizzatti offers Semiwiki readers a two-part series on why three kinds of hardware-assisted verification engines are now a must have for semiconductor designs continues today. His interview below with Juergen Jaeger, Prototyping Product Strategy Director in the Scalable Verification Solution division at Siemens EDA,… Read More

Tag: Juergen Jaeger

Verifying 10+ Billion-Gate Designs Requires Distinct, Scalable Hardware Emulation Architecture

In a two-part series, Lauro Rizzatti examines why three kinds of hardware-assisted verification engines are a must have for today’s semiconductor designs. To do so, he interviewed Siemens EDA’s Vijay Chobisa and Juergen Jaeger to learn more about the Veloce hardware-assisted verification systems.

What follows is part one,… Read More

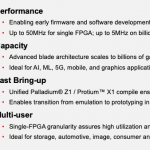

Cadence Releases Enterprise-Level FPGA Prototyping

Big prototyping hardware is essential to modern firmware and software development for pre-silicon, multi-billion gate hardware. For hardware verification it complements emulation, running fast enough for realistic testing on big software loads while still allowing fast-switch to emulation for more detailed debug where… Read More