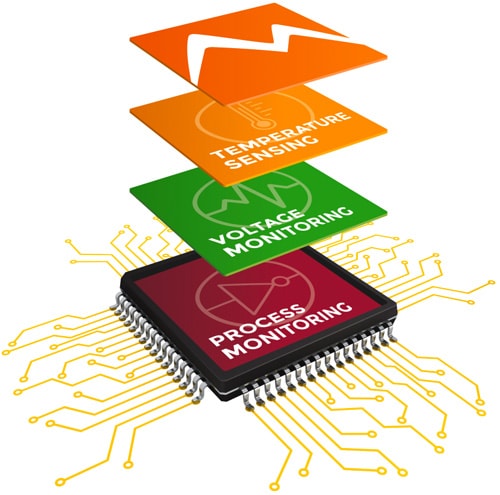

Designers spend plenty of time analyzing the effects of process, voltage and temperature. But everyone knows it’s not enough to simply stop there. Operating environments are tough and have lots of limitations, especially when it comes to power consumption and thermal issues. Thermal protection and even over-voltage protections… Read More

Tag: in-chip monitoring

Siemens Acquires UltraSoC to Drive Design for Silicon Lifecycle Management

As reported recently by Dan Nenni, Siemens has signed an agreement to acquire Cambridge, UK-based UltraSoC Technologies Ltd. We’ve all seen plenty of mergers and acquisitions in EDA. Some transactions perform better than others. The best ones enhance an existing product or service by blending non-overlapping technologies.… Read More

Data Centers and AI Chips Benefit from Embedded In-Chip Monitoring

Webinars are a quick way to come up to speed with emerging trends in our semiconductor world, so I just finished watching an interesting one from Moortec about the benefits of embedded in-chip monitoring for Data Center and AIchip design. My first exposure to a data center was back in the 1960s during an elementary school class where… Read More

Improving Yield and Reliability with In-Chip Monitoring, there’s an IP for that

There’s an old maxim that you can only improve what you measure, so quality experts have been talking about this concept for decades and our semiconductor industry has been the recipient of such practices to such an extent that we can now buy consumer products that include chips with over 5 billion transistors in them. You’ve… Read More

Making Your Next Chip Self-Aware

One holy grail of AI software developers is to create a system that is self-aware, or sentient. A less lofty goal than sentient AI is for chip designers to know how each specific chip responds to Process variations, Voltage levels and Temperature changes. If a design engineer knew exactly which process corner that each chip was fabricated… Read More