One of the surprises at DAC for ICScape was to be listed on Gary Smith’s list of companies to see. Surprised, since ICScape had never presented their products to him. They were listed under design debug. They don’t have a single product that really falls under that description, but rather a family of tools under the ICExplorer… Read More

Tag: icscape

How Good Is Your Library? Are You Sure?

One task that is not very exciting but is critical is that of library quality assurance. Many design groups have created their own procedures, often having been burned in the past, to ensure that the libraries that they use are good. Failure to do so has resulted in:… Read More

How Good Are Your Clocks?

One of the trickiest tasks in designing a modern SoC is getting the clock tree(s) right. The two big reasons for this:

- the clocks can consume 30% or more of the power of the whole chip, so minimizing the number of buffers inserted is critical to keeping power under control

- the clock insertion delay and clock skew have a major impact on

What is Skipper?

What is Skipper? Well, it seems it’s a penguin in the movie Madagascar. And one of Barbie’s sisters. Who knew? But for Semiwiki readers it’s an integrated chip finishing platform from ICScape. Skipper can read in full-chip layout extremely fast, examine it and manipulate it in various ways, and write it out again.… Read More

EDA Tools from China at DAC

Last year I was surprised at DAC by an un-heard of EDA company from China, ICScape. This year I followed up and spoke with Ravi Ravikumar about what’s new with ICScape in 2013.… Read More

SemiWiki Top 10 Must See @ #50DAC List!

This list was compiled by the SemiWiki bloggers highlighting emerging technologies that we have written about and that will be demonstrated at the Design Automation Conference next week. We highly recommend you investigate them further during your time in Austin and please let us know what you think.

Today SemiWiki has more than… Read More

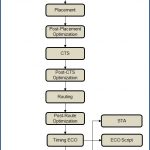

Efficient Handling of Timing ECOs

Today, in the design of any type of system on chip (SoC), timing closure is a major problem and it only gets worse with each new, and more advanced process technology. Timing closure is closely inter-leaved with power and clock design. The complexity of achieving closure rises sharply with increasing design density and advancing… Read More

CEO Interview: Jason Xing of ICScape Inc.

I recently had the opportunity to interview Jason Xing, Ph.D., CEO and President of ICScape, Inc. Below is a subset of the nearly two hour long interview.

How did you first become involved in EDA?

My EDA career started in the mid-90s when I started working on my PhD thesis at the University of Illinois in Urbana-Champaign. My thesis… Read More

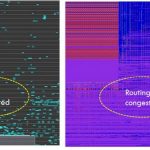

Modern SoC designs require a placement- and routing-aware ECO solution to close timing

As an applications engineer for over 15 years supporting physical design tools that enable implementation closure, I have seen the complexity of timing closure grow continuously from one process node to the next. At 28nm, the number of scenarios for timing sign-off has increased to the extent that is way beyond the number that … Read More

Properly Handing Of Clock Tree Synthesis Specifications

Given today’s design requirements with respect to low power, there is increasing focus on the contribution to total power made by a design’s clock trees. The design decisions made by the front-end team to achieve high performance without wasting power must be conveyed to back-end team. This hand-off must be accurate… Read More