You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

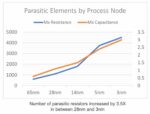

With advanced semiconductor processes continuing to shrink, the number and complexity of parasitic elements in designs grows exponentially contributing to one of the most significant bottlenecks in the design flow. Undetected parasitic-induced issues can be extremely costly, often resulting in tape-out delays.

Silvaco… Read More

IC designs have physical verification applications like Layout Versus Schematic (LVS) at the transistor-level to ensure that layout and schematics are equivalent, in addition there’s an Electrical Rules Check (ERC) for connections to well regions called a soft check. The connections to all the devices needs to have the most… Read More

Humans certainly have always had an aesthetic preference for symmetry. We also see symmetry showing up frequently in nature. The importance of symmetry in electronic designs has been apparent for decades. There are a host of analog structures that require balanced layout. For instance, these include differential pairs and … Read More

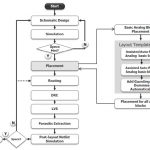

Digital IC design has been largely automated with high-level languages, RTL coding, logic synthesis, and automated place and route tools. What about analog IC layout automation, is it possible? A few EDA companies think that it is possible and even practical. In recent memory there were two companies really focused on analog … Read More

Timing closure is a “tortoise” for some system-on-chip (SoC) designers just the way many digital guys call RF design a “black art”. Chip designers often tell horror stories of doing up to 20 back-end physical synthesis place & route (SP&R) iterations with each iteration taking a week or more. “Timing closure”, a largely… Read More

Synopsys has been acquiring EDA and IP companies at a fast clip over the past few years and it’s often made me wonder how they are going to craft a coherent tool flow for custom IC design. At DACthis year I learned that for schematic capture the winning tool is Custom Designer SE– a relatively new tool, while the IC layout… Read More

Last Monday at DAC I met with Linda Fosler, Marketing Director at Mentor Graphics to get an update on what’s new with Eldo(Circuit simulator) and Pyxis (custom IC layout and schematic).

Linda Fosler, Mentor Graphics… Read More

Daniel Payne recently blogged some of the integration challenges facing Synopsys with their impending acquisition of SpringSoft. On my way back from San Diego last week I stopped by Tanner EDA to discuss an alternative tool flow for users who find themselves concerned about the Laker Custom Layout road map.

Design of the analog… Read More

Linda Fosler, Tom Daspit and Mitch from Mentor Graphics met with me last Monday at DAC to provide an update on IC layout and circuit simulation tools. My notes follow:

Overview – Pyxis for Schematic and Layout, IC Station is re-branded as Pyxis. (Pyxis schematic is still Falcon, Ample language is still used.)… Read More