Verification is always a top priority for any chip project. Re-spins result in lost time-to-market and significant cost overruns. Chip bugs that make it to the field present another level of lost revenue, lost brand confidence and potential costly litigation. If the design is part of the avionics or control for an aircraft, the… Read More

Tag: do-254

Sigasi at the 2024 Design Automation Conference

Sigasi® will demonstrate its Sigasi Visual HDL™ (SVH™) portfolio during DAC, showing how it supports the shift-left methodology for chip design, catching specification errors early in the design cycle and fixing the inefficient HDL-based design flow.

The traditional HDL workflow cannot accommodate the massive amounts of… Read More

Something new in High Level Synthesis and High Level Verification

As SoC complexities continue to expand to billions of transistors, the quest for higher levels of design automation also rises. This has led to the adoption of High-Level Synthesis (HLS), using design languages such as C++ and SystemC, which is more productive than traditional RTL design entry methods. In the RTL approach there… Read More

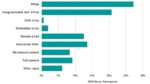

The State of FPGA Functional Verification

Earlier I blogged about IC and ASIC functional verification, so today it’s time to round that out with the state of FPGA functional verification. The Wilson Research Group has been compiling an FPGA report every two years since 2018, so this marks the third time they’ve focused on this design segment. At $5.8 billion… Read More

Formal Methods for Aircraft Standards Compliance

When promoting adoption of formal methods in functional verification, there are two hurdles to overcome: one technical, the other people. The first is a comfortable and familiar challenge for us engineers. Take the course, pass the test, get the certificate. Very mechanical and deterministic. People on the other hand are non-deterministic… Read More

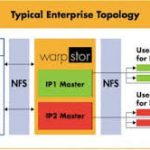

WEBINAR: Lightspeed Data Sync – Design Workspace Problems Solved!

With every process node and every SOC design, engineering and IT teams are experiencing an unprecedented data explosion. User workspaces routinely exceed 10’s of GB and sometimes even 100’s of GB. Regression runs, characterization runs, design and debug of workspaces, building verification environments – all of these… Read More

The DIY Syndrome

When facing a new design objective, we check off all the established tools and flows we know we are going to need. For everything else, we default to an expectation that we will paper over the gaps with scripting, documentation and spreadsheets. And why not? When we don’t know what we will have to deal with, in documentation, scheduling,… Read More

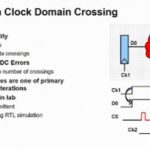

CDC Verification for FPGA – Beyond the Basics

FPGAs have become a lot more capable and a lot more powerful, more closely resembling SoCs than the glue-logic we once considered them to be. Look at any big FPGA – a Xilinx Zynq, an Intel/Altera Arria or a Microsemi SmartFusion; these devices are full-blown SoCs, functionally different from an ASIC SoC only in that some of the device… Read More

Updated tool cuts through DO-254 V&V chaos

Audits. The mere mention of the word keeps project managers up at night and sends most designers running. However, in the case of FPGA designs seeking DO-254 compliance, the product doesn’t ship until the audit is complete – there is no avoiding it, or skating around it.… Read More

Real FPGAs don’t eat fake test vectors

Vector blasting hardware is as old as digital test methodology itself. In the days of relatively simple combinational and finite state machine logic, a set of vectors aimed broadside at inputs could shake loose most faults with observable outputs. With FPGAs, creating an effective set of artificial test vectors has become a lot… Read More