I had the opportunity to preview an upcoming webinar on SemiWiki that deals with design robustness for signoff regarding advanced node digital designs (think single-digit nanometers). “Design robustness” is a key term – it refers to high quality, high yielding SoCs that come up quickly and reliably in the target system. We all… Read More

Tag: digital design

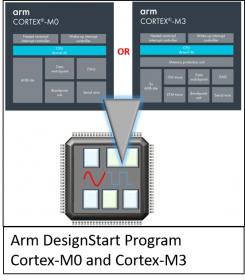

Arm and Mentor Use DesignStart Program to Accelerate Proof-of-Concept for IoT Designs

Sometimes the hardest thing about bringing a new idea to fruition is overcoming the inertia to get started with a proof-of-concept. You must be able to put together enough parts of the solution to prove to those controlling budgets that an idea has merit and is worth taking to the next level. It’s a bit of a chick-vs-egg scenario as … Read More

Digital, Analog, Software, IP – Isn’t it all just the same?

Designing an SoC requires a team, and the engineers typically use lots of specialized EDA software and semiconductor IP to get the job done. Many have started to ask about how designing a chip is different than designing and managing a large software project, or how is analog design different than digital design in terms of managing… Read More

TSMC’s 16FinFET and 3D IC Reference Flows

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

Addressing the Nanometer Digital Design Challenges! (Webinars)

Optimizing logical, physical, electrical, and manufacturing effects, Cadence digital implementation technology eliminates iteration without sacrificing design quality by addressing timing sensitivity, yield variation, and leakage power from the start. … Read More