You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

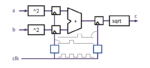

The Role of Clock Gatingby Steve Hoover on 11-28-2022 at 10:00 amCategories: EDA

Perhaps you’ve heard the term “clock gating” and you’re wondering how it works, or maybe you know what clock gating is and you’re wondering how to best implement it. Either way, this post is for you.

Why Power Matters

I can’t help but laugh when I watch a movie where the main characters are shrunk… Read More

For decades, tracing back to the days of Deming, the way to tackle complex engineering problems has been the pareto chart. Charting conditions and their contribution to the problem leads to mitigation priorities.

In the case of SoC power management, the old school pareto chart said the processor core was the biggest power hog and… Read More

Processor cores used in computers and smartphones have become impaired by their own complexity and can’t fully utilize future CMOS generations for increasing their efficiency. Due to the continued increase of density and speed of transistors, these big cores produce too much heat per mm[SUP]2[/SUP] if trying to follow Moore’s… Read More

Dark Siliconby Paul McLellan on 05-26-2014 at 5:29 pmCategories: IP, Sonics

One of the problems with chips today is that of so-called “dark silicon”. We can put massive functionality on an SoC today. A billion transistors, and that is just at 28nm. But power constraints (both leakage and dynamic power) limit how much of the chip can be powered up at any one time. In some cases this is not that big… Read More