If you have ever send a Request For Quotation (RFQ) for an ASIC including processor IP core, memories, Interfaces IP like PCIe, SATA or USB and Analog function like Analog to Digital Converter (ADC) or Digital to Analog Converter (DAC), you have discovered, like I did a couple of years ago, that these Analog functions may be the key… Read More

Tag: dac

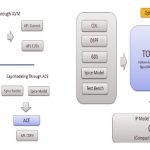

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

SoC Constraints, Design & Verification at DAC

I hadn’t followed EDA start-up company Ausdiamuch before, so at DAC I met with Sam Appleton, CEO to find out what they are all about.

Sanjay Lall, Sam Appleton – Ausdia

… Read More

Design Test and Regression Management of SoCs

Eric Peersfounded Missing Link tools in 2008 and his company was acquiredby Methodics in 2012, so I met with him at DAC to understand how their EDA tools for Design, Test and Regression Management are used in an SoC design.

Eric Peers, Methodics… Read More

Speeding Design Closure at DAC

At DAC you can measure buzz by how many people are crowded into your booth. I saw a crowd at the Oasys booth, so stopped to take in their 10 minute overview presentation. Here’s what I learned.… Read More

Analysis of Power, Thermal, EM, IR at DAC

Most EDA start-up companies have a narrow product focus to complement existing tool flows, however Invarian is taking a much bolder approach by offering tools for:

- Power analysis

- Thermal analysis

- EM / IR analysis

- 3D Thermal analysis

Analog FastSPICE at DAC

Berkeley DA coined the phrase “Analog FastSPICE”, and I’ve been getting an update from them at DAC for several years now. In Austin I met with Paul Estradathe COO and Patrick Muyshondt.

Paul Estrada

Paul Estrada, COO (circa 2010)

… Read More

HW Prototyping and HLS at DAC

I love it when EDA companies send their engineers to DAC because I learn more of the unvarnished truth about their products. I met with Bill Thomas of Aldec to get an update on their HW prototyping boards, then two NEC engineers to learn about High Level Synthesis.

HW Prototyping

Bill Thomas, Research Engineer at Aldec

… Read More

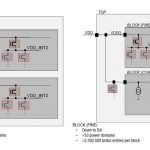

A 3D Field Solver for Parasitic Extraction Thermal ESD Analysis

The smaller the process node the more necessary it is that you extract accurate parasitics from interconnect and 3D structures in order to analyze timing, thermal effects and ESD compliance. Silicon Frontlinehas EDA tools in all three of these categories, so I met with Dermott Lynchat DAC to get an annual update.

Dermott Lynch,… Read More