At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

Tag: cowos

Elevating AI with Cutting-Edge HBM4 Technology

Artificial intelligence (AI) and machine learning (ML) are evolving at an extraordinary pace, powering advancements across industries. As models grow larger and more sophisticated, they require vast amounts of data to be processed in real-time. This demand puts pressure on the underlying hardware infrastructure, particularly… Read More

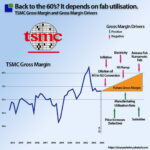

TSMC’s Business Update and Launch of a New Strategy

What looks like a modest market expansion strategy is all but modest.

Insights into the Semiconductor Industry and the Semiconductor Supply Chain.

As usual, when TSMC reports, the Semiconductor industry gets a spray of insights that help understand what goes on in other areas of the industry. This time, TSMC gave more insight … Read More

TSMC Advanced Packaging Overcomes the Complexities of Multi-Die Design

The TSMC Technology Symposium provides a worldwide stage for TSMC to showcase its advanced technology impact and the extensive ecosystem that is part of the company’s vast reach. These events occur around the world and the schedule is winding down. TSMC covers many topics at its Technology Symposium, including industry-leading… Read More

What’s all the Noise in the AI Basement?

My dog yawns every time I say Semiconductor or Semiconductor Supply Chain. Most clients say, “Yawn…. Don’t pontificate – pick the Nasdaq winners for us!”

Will Nvidia be overtaken by the new AI players?

If you follow along with me, you might gain some insights into what is happening in AI hardware. I will leave others to do the… Read More

UCIe InterOp Testchip Unleashes Growth of Open Chiplet Ecosystem

Intel recently made headlines when CEO Pat Gelsinger unveiled the world’s first UCIe interoperability test chip demo at Innovation 2023. The test chip built using advanced packaging technology is codenamed Pike Creek and is used to demonstrate interoperability across chiplets designed by Intel and Synopsys. More details … Read More

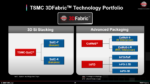

TSMC 2023 North America Technology Symposium Overview Part 3

TSMC’s 3DFabric initiative was a big focus at the symposium, as it should be. I remember when TSMC first went public with CoWos the semiconductor ecosystem, including yours truly, let out a collective sigh wondering why TSMC is venturing into the comparatively low margin world of packaging. Now we know why and it is absolutely… Read More

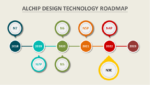

Alchip Technologies Offers 3nm ASIC Design Services

Throughout its history, the ASIC industry has had its ups and downs. With feast and famine cycles, the ASIC business model is not for the faint of heart. Some companies tread boldly while others dread the cycles and stay away from this business model. Those who are consistently successful have to overcome many challenges thrown … Read More

TSMC 2022 Technology Symposium Review – Advanced Packaging Development

TSMC recently held their annual Technology Symposium in Santa Clara, CA. The presentations provide a comprehensive overview of their technology status and upcoming roadmap, covering all facets of the process technology and advanced packaging development. This article will summarize the highlights of the advanced packaging… Read More

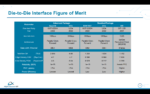

Die-to-Die IP enabling the path to the future of Chiplets Ecosystem

The topic of chiplets is getting a lot of attention these days. The chiplet movement has picked up more momentum since Moore’s law started slowing down as process technology approached 5nm. With the development cost of a monolithic SoC crossing the $500M and wafer yields of large die-based chips dropping steeply, the decision … Read More